Working draft

Valeriy Vyatkin

## Modelling and Verification of Discrete Control Systems with Net Condition/Event Systems and Visual Verification Framework

All rights reserved, ©, V. Vyatkin, 2007-2012, Auckland Version 1/15/2012

## Disclaimer

This text is a working draft and may contain some fragments earlier published in papers co-authored with other researchers, in particular with Hans-Michael Hanisch from Martin-Luther University of Halle (Germany), Jose LM Lastra and Andrei Lobov from Tampere University of Technology, (Finland), Gustavo Bouzon from University of Santa – Catharina (Brazil) whose contribution and collaboration is greatly acknowledged and appreciated.

The author is very much grateful to Cheng Pang for valuable contributions to this document, especially for the graphical material in Chapter 11.

The author will be grateful for any comments. Please report to v.vyatkin@auckland.ac.nz

## **Table of Contents**

| D  | Disclaimer                                                           |                                                     |    |  |  |  |

|----|----------------------------------------------------------------------|-----------------------------------------------------|----|--|--|--|

| Та | Table of Contents   3                                                |                                                     |    |  |  |  |

| St | Structure of the text                                                |                                                     |    |  |  |  |

| 1  | I Introduction: modelling and verification of cyber-physical systems |                                                     |    |  |  |  |

|    | 1.1                                                                  | Supporting Tool Framework                           | 10 |  |  |  |

|    | 1.2                                                                  | History of NCES developments                        | 11 |  |  |  |

| 2  | Sign                                                                 | nal/Event Nets                                      | 14 |  |  |  |

|    | 2.1                                                                  | Introduction                                        | 14 |  |  |  |

|    | 2.2                                                                  | Syntax                                              | 14 |  |  |  |

|    | 2.3                                                                  | Semantics                                           | 15 |  |  |  |

|    | 2.4                                                                  | Conflicts and non-determinism                       | 17 |  |  |  |

|    | 2.5                                                                  | Condition arcs                                      | 18 |  |  |  |

|    | 2.6                                                                  | Arcs with capacities (weights)                      | 18 |  |  |  |

|    | 2.7                                                                  | State and reachability                              | 19 |  |  |  |

|    | 2.8                                                                  | State transition modes                              | 20 |  |  |  |

|    | 2.9                                                                  | Synchronous transitions                             | 21 |  |  |  |

|    | 2.10                                                                 | Transitions without incoming arcs                   | 24 |  |  |  |

|    | 2.11                                                                 | Priorities                                          | 24 |  |  |  |

|    | 2.12                                                                 | Firing rules                                        | 24 |  |  |  |

| 3  | Moo                                                                  | dular S/E Nets = Net Condition/Event Systems        | 26 |  |  |  |

|    | 3.1                                                                  | Encapsulation of models into modules                | 26 |  |  |  |

|    | 3.2                                                                  | Model type definition                               | 27 |  |  |  |

|    | 3.3                                                                  | Typed NCES                                          | 28 |  |  |  |

|    | 3.4                                                                  | Capacities of condition arcs                        | 29 |  |  |  |

|    | 3.5                                                                  | Benefits of NCES                                    | 30 |  |  |  |

| 4  | Sem                                                                  | nantics of Modular Models                           | 33 |  |  |  |

|    | 4.1                                                                  | A condition/event input of a module is not assigned | 33 |  |  |  |

|    | 4.2                                                                  | Multiple arc assignments to a module's input/output | 34 |  |  |  |

|    | 4.2.1                                                                | Condition arc weights between modules               | 35 |  |  |  |

|    | 4.2.2 | 2 Several condition arcs originating in the same place          | 35   |

|----|-------|-----------------------------------------------------------------|------|

|    | 4.2.2 | 3 Visual Verifier support of non-assigned module inputs         | . 36 |

| 5  | Tim   | ed models                                                       | 38   |

|    | 5.1   | Discrete timing                                                 | 38   |

|    | 5.2   | Firing rules in TNCES                                           | . 39 |

|    | 5.3   | Implementation                                                  | 42   |

|    | 5.4   | Restrictions                                                    | 42   |

| 6  | Mo    | delling of closed-loop controller-plant systems                 | 43   |

| 7  | Bas   | ics of Plant Process Modelling                                  | 46   |

|    | 7.1   | Processes                                                       | 46   |

|    | 7.2   | Simple process model                                            | 46   |

|    | 7.3   | Process with exception                                          | 47   |

|    | 7.4   | Two time scales: ticks in controller and time-elapsing in plant | 47   |

| 8  | Mo    | delling Control Programs                                        | 49   |

|    | 8.1   | Data storage and assignment                                     | 50   |

|    | 8.2   | Linear sequence of commands                                     | 50   |

|    | 8.3   | Conditional choice                                              | 51   |

|    | 8.4   | Boolean operations                                              | 52   |

|    | 8.5   | Subroutine call                                                 | 53   |

| 9  | Co-   | existence of synchronous and asynchronous behaviour             | 55   |

|    | 9.1   | Non-timed models                                                | 56   |

|    | 9.2   | Timed models                                                    | 57   |

|    | 9.3   | Testing timed NCES modules                                      | 58   |

| 1( | ) Cor | nplete Example: Cylinder control                                | 59   |

|    | 10.1  | Object description                                              |      |

|    | 10.2  | Modelling the plant: Linear drive                               | 60   |

|    | 10.3  | Deadlocks                                                       | 66   |

|    | 10.4  | Branching                                                       | 68   |

|    | 10.5  | Deeper analysis                                                 | 69   |

|    | 10.6  | Exercises                                                       |      |

|    | 10.7  | Review questions                                                | 69   |

|    |       |                                                                 |      |

| 11 Mo  | del Verification with Visual Verifier                 | . 70 |

|--------|-------------------------------------------------------|------|

| 11.1   | Visual Verifier functions                             | . 70 |

| 11.2   | Data formats                                          | . 72 |

| 11.3   | Limitations                                           | . 73 |

| 11.4   | A hint for clearer models                             | . 74 |

| 12 Use | r Interface of Visual Verifier                        | . 77 |

| 12.1   | Tabs                                                  | . 77 |

| 12.1   | .1 Functional toolbars                                | . 78 |

| 12.2   | Typical sequence of steps using Visual Verifier       |      |

| Step   | 1: Open the header file of the model                  | . 79 |

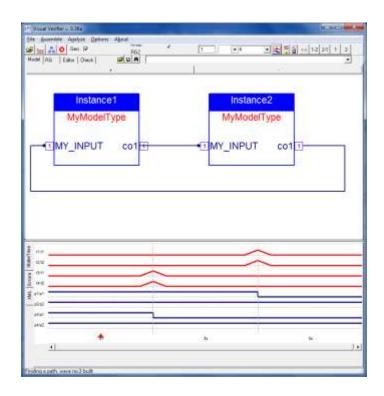

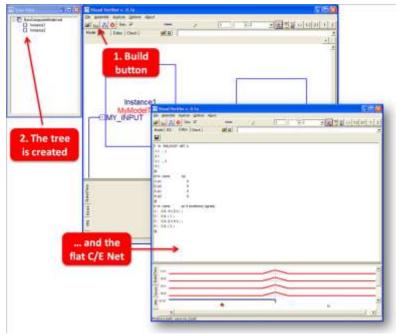

| Step   | 2: Build a flat Condition-Event net model             | . 80 |

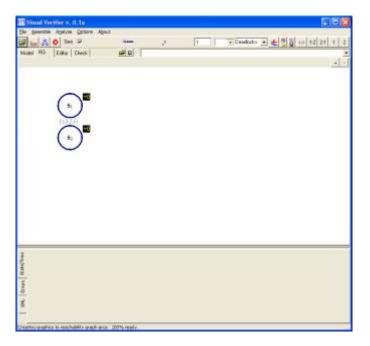

| Step   | b3: Generate reachability space of the flat S/E model | . 81 |

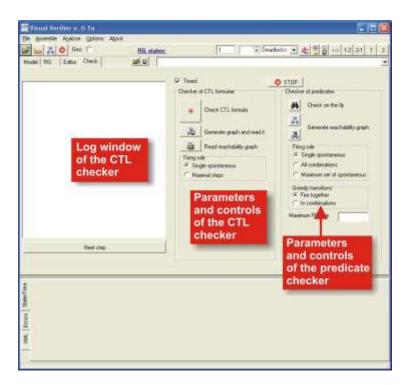

| Step   | 4. Check specifications using internal model checker  | . 82 |

| 12.3   | Model-checkers                                        | . 82 |

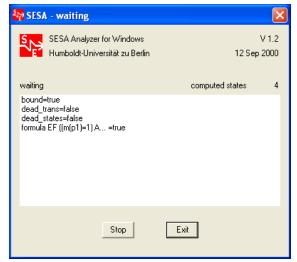

| 12.4   | Command line SESA                                     | . 83 |

| 12.5   | SESA from ViVe                                        | . 84 |

| 12.6   | Hints for analysing complex models                    | . 86 |

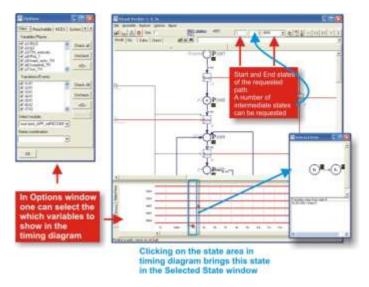

| 12.7   | Exploring reachability space                          | . 87 |

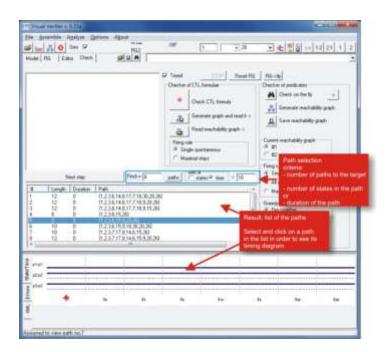

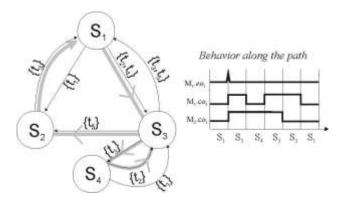

| 12.8   | Finding paths satisfying certain criteria             | . 89 |

| 12.9   | Metrics                                               | . 89 |

| 13 Ver | ification of Properties                               | . 91 |

| 13.1   | Overview                                              | . 91 |

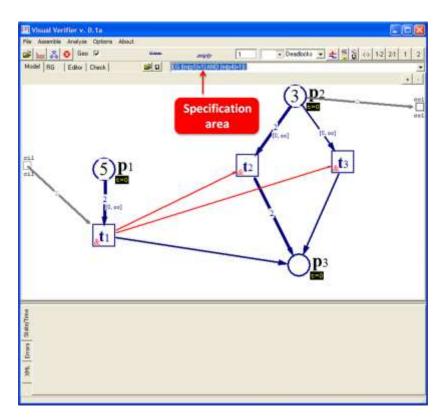

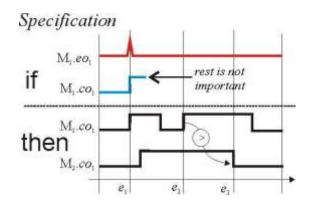

| 13.2   | Syntax of specifications                              | . 93 |

| 13.3   | How to check specifications                           | . 93 |

| 14 Dis | tributed controllers                                  | . 96 |

| 14.1   | Discrete-state model                                  | . 96 |

| 14.2   | Timed model                                           | . 97 |

| 14.3   | Using synchronous transitions                         | . 99 |

| 14.4   | Synchro sets in ViVe                                  | . 99 |

| 14.5   | Example of different firing rules application         | 100  |

| 14.5   | 5.1 Non-timed                                         | 100  |

| 14.5   | 5.2 Timed                                             | 101  |

|        |                                                       |      |

| 14.6   | Model modification: synchronous transitions      |   |

|--------|--------------------------------------------------|---|

| 14.6   | 5.1 Non-timed                                    |   |

| 14.6   | 5.2 Timed                                        |   |

| 14.7   | Modelling communicating processes                |   |

| 15 Exa | ample of a distributed system: two cylinders     |   |

| 15.1   | Reusing original controllers                     |   |

| 15.2   | Finding collision                                |   |

| 15.3   | Block – permit protocol                          |   |

| 15.4   | Central controller                               |   |

| 15.5   | Exercises                                        |   |

| 16 Mo  | delling Programmable Logic Controllers (PLCs)    |   |

| 16.1   | System routines                                  |   |

| 16.2   | Ladder logic                                     |   |

| 17 Mo  | delling of Complex Plants                        |   |

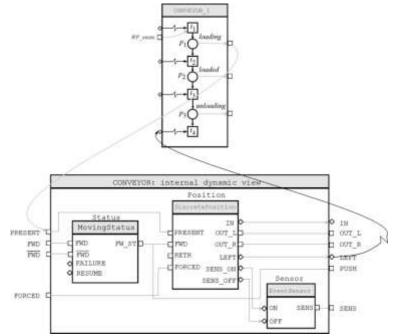

| 17.1   | Process/Sensor model                             |   |

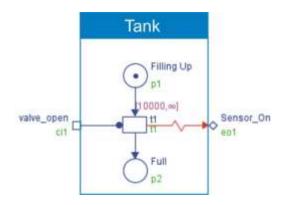

| 17.2   | Tank                                             |   |

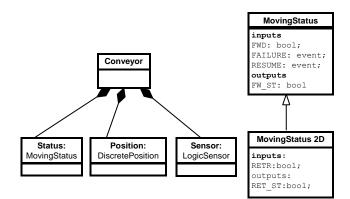

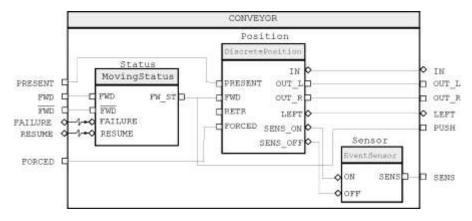

| 17.3   | Conveyor                                         |   |

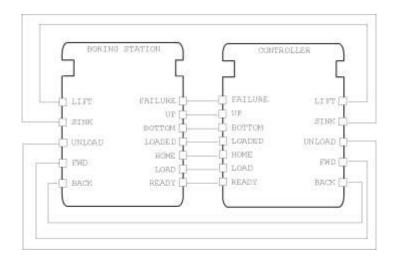

| 17.4   | Boring station                                   |   |

| 17.4   | 1.1 S/E Net model of a Boring Station            |   |

| 17.4   | 4.2 Controller                                   |   |

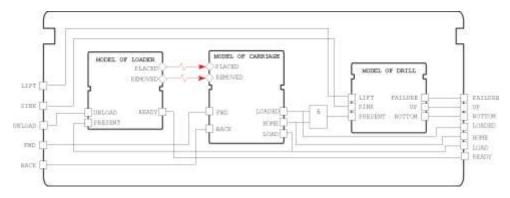

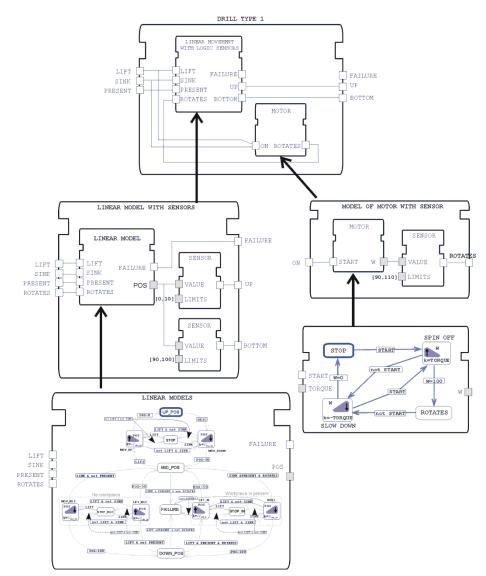

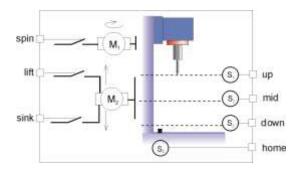

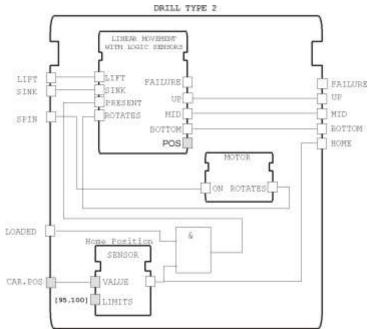

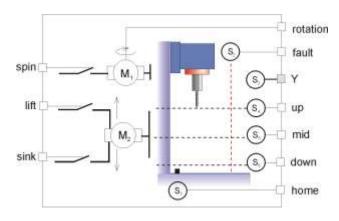

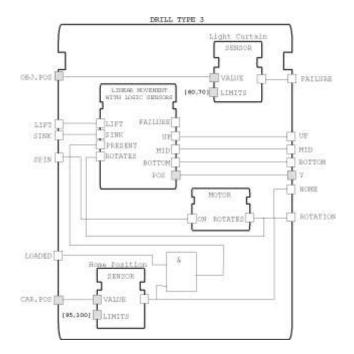

| 17.5   | Model of Drill                                   |   |

| 17.6   | Variations                                       |   |

| 17.6   | 5.1 Enhanced Drill                               |   |

| 17.6   | 5.2 Advanced Drill                               |   |

| 17.7   | Modelling dynamic and logic of processes         |   |

| 17.8   | Verification model in NCES                       |   |

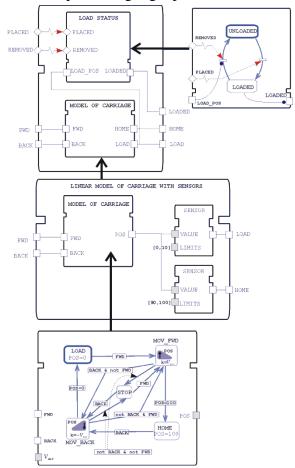

| 17.9   | Carriage                                         |   |

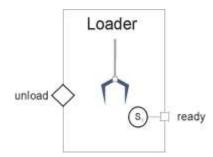

| 17.10  | Loader                                           |   |

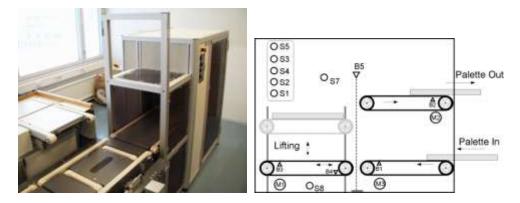

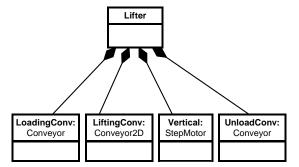

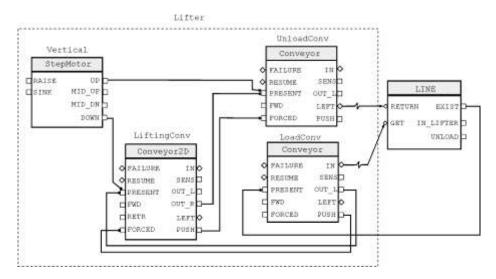

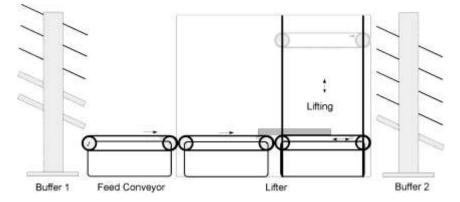

| 17.11  | Lifter                                           |   |

| 17.12  | Examples of specifications of Lifter's behaviour |   |

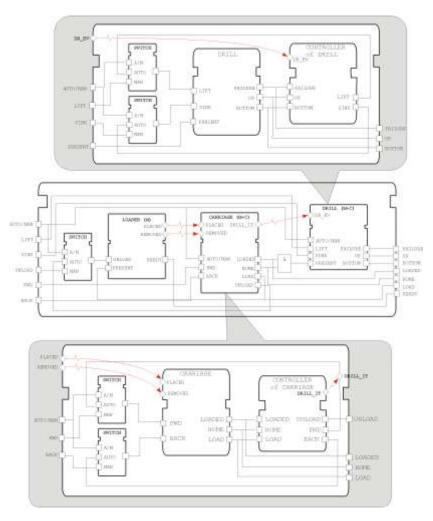

| 18 Mu  | lti-level model design pattern                   |   |

|        |                                                  | 6 |

| 18.1 Hierarchies in models                              |           |  |  |  |  |

|---------------------------------------------------------|-----------|--|--|--|--|

| 18.2 Motivation                                         |           |  |  |  |  |

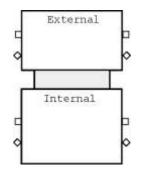

| 18.3 Notation of the two-level modules                  |           |  |  |  |  |

| 19 Specifications using Timing Diagrams                 |           |  |  |  |  |

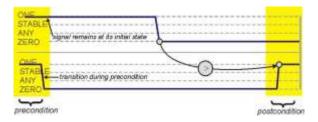

| 19.1 Timing Diagrams for specification                  |           |  |  |  |  |

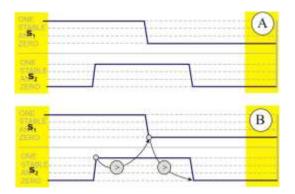

| 19.1.1 Definitions                                      |           |  |  |  |  |

| 19.1.2 Specified Signals                                |           |  |  |  |  |

| 19.1.3 Event Ordering in Different S                    | ignals152 |  |  |  |  |

| 19.1.4 Specification of Finite Behavi                   | our153    |  |  |  |  |

| 19.1.5 Specification of infinite behav                  | viour     |  |  |  |  |

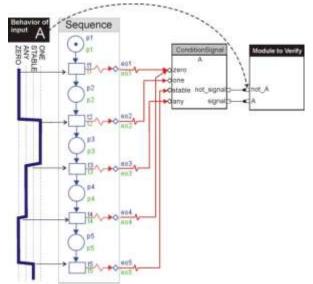

| 19.2 NCES Model of Timing Diagrams                      |           |  |  |  |  |

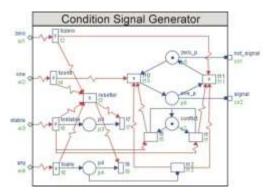

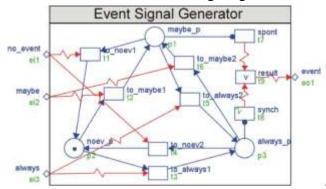

| 19.2.1 Event Generator                                  |           |  |  |  |  |

| 19.2.2 Signal Generation Module                         |           |  |  |  |  |

| 19.3 Program Implementation                             |           |  |  |  |  |

| Annex 1: XML format of Condition/Event N                | lets 160  |  |  |  |  |

| Example of a basic module made in TNCES editor          |           |  |  |  |  |

| XML of a "composite" NCES block                         |           |  |  |  |  |

| Annex 2: More formal definition of Condition/Event Nets |           |  |  |  |  |

| 19.4 NCES definition                                    |           |  |  |  |  |

| 19.5 C/E Net definition                                 |           |  |  |  |  |

| 19.5.1 Set theoretical definition                       |           |  |  |  |  |

| 19.5.2 State of C/EN model                              |           |  |  |  |  |

| 19.5.3 Firing rules                                     |           |  |  |  |  |

| 19.5.4 Step and state transitions                       |           |  |  |  |  |

| Annex 3. CTL syntax of SESA                             |           |  |  |  |  |

| CHARACTERS                                              |           |  |  |  |  |

| TOKENS                                                  |           |  |  |  |  |

| PRODUCTIONS                                             |           |  |  |  |  |

| Annex 4: Command line SESA parameters                   |           |  |  |  |  |

| References                                              |           |  |  |  |  |

## Structure of the text

First part (Chapters 1-5) introduces the framework and modelling language of Net Condition/Event Systems (NCES) as follows. Chapter 1 introduces the formal verification framework. Chapter 2 starts with providing informal introduction into the formalism of Signal/Event nets. Chapter 3 introduces modular Signal/Event nets called Net Condition/Event Systems. Chapter 4 discusses some challenges to the S/E net semantics brought by the modularity of NCES, and Chapter 5 adds time to the Signal/Event nets.

Second part (Chapters 6-12) presents basics of modelling automation systems and technique of their formal verification in the Visual Verification Framework as follows. Chapter 6 introduces the framework of closed-loop modelling and verification, Chapter 7 presents some basic techniques for modelling objects and physical processes (plant) using NCES, Chapter 8 introduces basic NCES elements to be used in controller models, such as models of variables and operations over them. Chapter 9 discusses some challenges arising from the need to combine purely deterministic and synchronous objects (controller) with asynchronous and non-deterministic processes (plant). Chapter 10 presents an example of a simple automation system modelled and verified in the presented framework. Chapter 11 considers the use of the **Visual Verifier** tool in more detail, and Chapter 12 presents more details on the properties to be verified.

The third part (Chapters 13-15) presents some additional techniques and facts and is structured as follows: Chapter 13 discusses specifics of distributed controller modelling. Modelling of Programmable Logic Controllers is exemplified in Chapter 14. Chapter 15 is devoted to systematic modelling of plants. Chapter 16 introduces the ideas of hierarchical model composition in NCES.

Annex 1 provides examples of XML representation of NCES models. Annex 2 contains more rigorous definitions of NCES.

# 1 Introduction: modelling and verification of cyber-physical systems

In computer science *formal verification* is an act of proving the correctness of programs by using mathematical methods and models. It can be used as an automatic alternative to the simulation-based testing and debugging, improving dependability and reliability of automation systems. Unlike testing via simulation, the formal verification can explore the complete set of system's state space and prove mathematically that no undesirable or dangerous behaviour occurs. This can reduce the effort spent on validation the same time increasing its quality which especially important in safety critical applications. Formal verification be also very helpful in proving the compliance with various certification requirements.

*Cyber-physical systems* is a novel view on embedded systems that takes into account the dynamics and the structure of the environment where the embedded device works. In many control and monitoring applications this view has proven to be beneficial as compared to a more narrow focus only on the computing hardware and software.

In particular, in control systems, usually the control software is the target of verification. This software is further referred to as *controller*, and it is the essential part of the embedded *control device* connected to the *plant under control*. Plant and controller form the interconnected closed-loop control system. For example, in industrial automation, the controller code usually is a variable part of the system, while the hardware remains unchanged. The controller can be programmed in one of general-purpose or specialized programming languages, e.g. following the IEC61131-3 standard [38].

- 1. The closed-loop system is modeled using an appropriate finite-state or hybrid formalism, e.g. finite state machines, Petri nets, etc. In *closed-loop modeling* the model of the plant needs to be present explicitly. It has to be designed manually by control engineers, while the model of the controller can be built automatically given the code. In *open-loop* modeling only the controller part is verified under some assumptions about its inputs.

- 2. The desired or forbidden behavior of the plant-controller system needs to be described in form of *specifications*, i.e. the properties to hold or to avoid. The specifications have to be formalized using a formal language compatible with the description of the model.

- 3. Given the model and a number of formal specifications, it can be formally checked whether the specifications hold with respect to the model. This process is called *model-checking*.

- 4. The results of the model-checking have to be interpreted in terms understandable by the engineers. For this purpose, a bi-directional mapping from the original system to its model and back has to be provided.

This text presents a framework for modelling and verification which is based on the formalism of Net Condition/Event Systems (NCES).

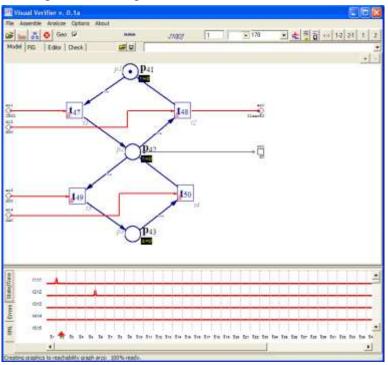

#### 1.1 Supporting Tool Framework

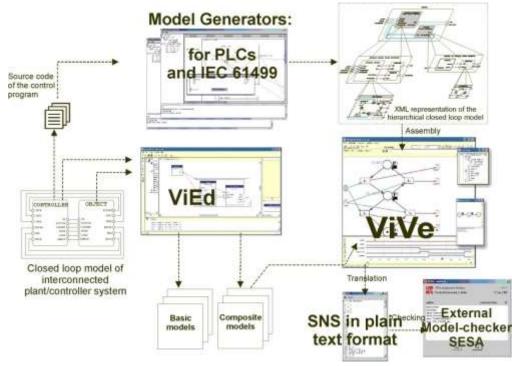

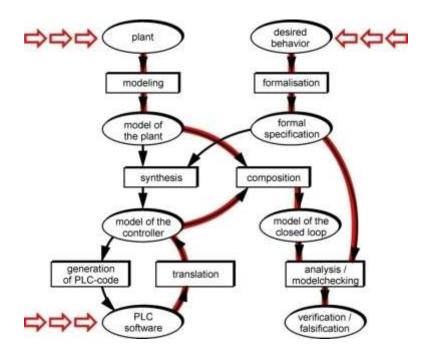

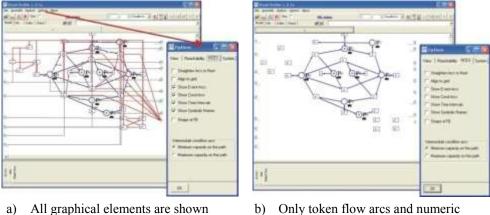

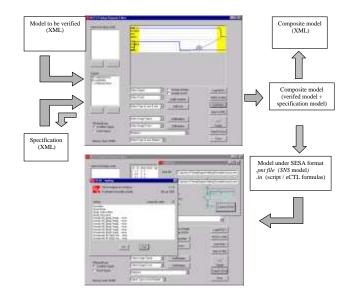

To facilitate the use of NCES by engineers, the formalism is supported by tools and methodologies. The framework is presented in Figure 1.

Figure 1. Tool framework for modelling and verification

The functions of the tools are as follows:

• Visual NCES editor (ViEd) providing full graphical authoring and editing of the models. Its manual is provided in a separate document;

- Visual Verifier (ViVe) an integrated tool that contains a model builder (assembler), a translator to the flat format for subsequent model-checking, interfaces to several model-checkers, and the means for analysis of scenarios (e.g. their visualization in form of state/time diagrams), or even system simulation along the selected scenarios.

- The model checker **SESA** allows for efficient model-checking of fairly complex systems (millions of discrete states);

- The application methodologies are represented as libraries of standard model elements and by the web-based documentation;

The NCES modelling language is open - an XML based data format allows the development of add-ons to the existing tools, for example model-generators for particular programming languages in which the controllers are programmed.

The graphical editor provides full graphical authoring and editing of the models. The editor uses an open XML-based data format for basic and composite NCES models. The data format of composite model blocks intentionally was made identical with that of IEC61499 function blocks, supported by tool (*FBDK*).

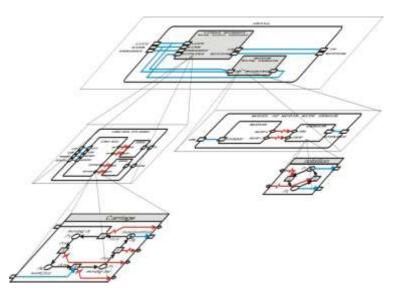

The integrated environment Visual Verifier inputs the model type files given in XML and is capable of:

- Assembling a composite, hierarchically organized model from modules contained in different libraries. The component model types are instantiated into NCES modules.

- Translating the model into a "flat" NCES with the through numbering of places and transitions. The inter-module connections are converted into event and condition arcs between places and transitions. Thus the module boundaries are removed and the model-checking tools can be applied. In particular, the translator generates files in the input format of SESA model checker.

To enjoy the benefits of graphical formalisms the model authoring and maintenance have to be supported in a visual intuitive way. The evolution of graphical tools is described in the following section.

#### **1.2 History of NCES developments**

The first version of the tool for editing Timed NCES (TNCES) for was implemented at the University of Halle, (Germany) as a template to **Visio** universal graphic editor. The editor supported only the non-typed approach which did not allow for convenient re-use of previously developed model components. The whole model needed to be developed from scratch and the re-use was possible only by "cut and paste" of some model elements.

Figure 2. Visio TNCES Template.

The need to re-use models pushed the development of an open XML-based data format for basic and composite NCES models. The data format of composite blocks was intentionally made identical with that of IEC61499 function blocks, supported by tools [17, 18]. Then the export to the XML format was added to the editor in order to create a model type out of a single NCES module. This way the former **Visio**-based editor could be used for populating the library of basic model types, while FBDK could be used for creating complex model types.

However, FBDK is lacking convenience in dealing with module connections. Besides the use of three software tools just for editing models is too complicated. For this reason another editor (ViEd) was conceived that integrates editing of basic and composite models in fully intuitive visual way.

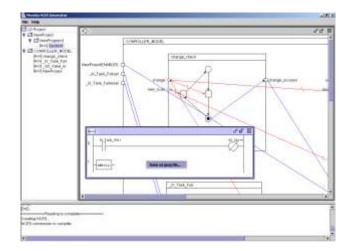

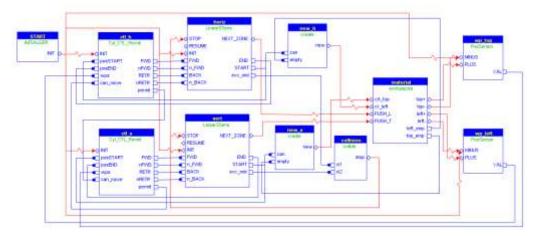

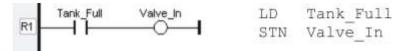

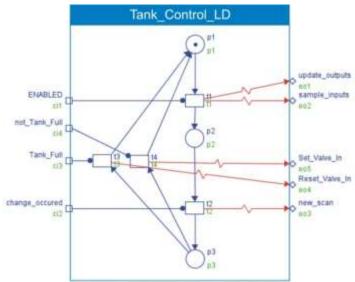

The model of a controller can be generated by the MOVIDA NCES Generator (Fig. 10). The generator takes as an input source code of controllers in several PLC programming languages (for example  $Omron^{TM}$ ) LD project represented as a textual file), converts it into TNCES, and saves the data in XML based format. The openness and self-explanatory XML representation simplifies the development of the tools that may work with TNCES.

Figure 3. MOVIDA NCES Generator.

## 2 Signal/Event Nets

#### 2.1 Introduction

In this chapter we give informal definition of Signal/Event nets (S/E nets). A more formal definition is presented in Annex 1 and in the document "Analyzing Signal / Event Nets" [21].

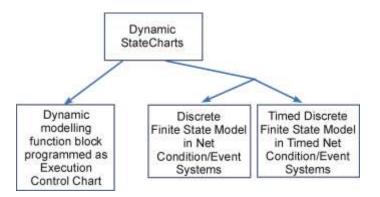

The formalism of Condition/Event systems, suggested by Sreenivasan and Krogh in (1990), provides a convenient framework for modular modelling of discrete-event systems. Internal content of modules can be different: so far finite state and hybrid automata [3, 4], as well as Petri net-like formalisms [7] have been studied in this role.

The Condition/Event model can serve to represent systems' interface abstractions, internal structure and behaviour of single elements. This model can be easily mapped then onto IEC61499 function blocks [23], thanks to many similarities, namely event and data interfaces and State Chart definition of functionality of single modules.

#### 2.2 Syntax

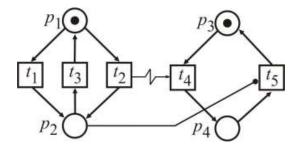

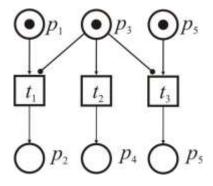

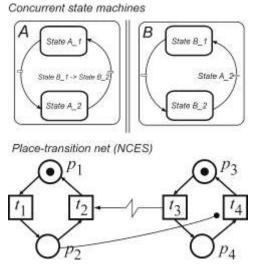

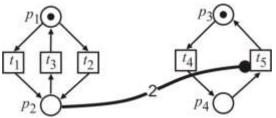

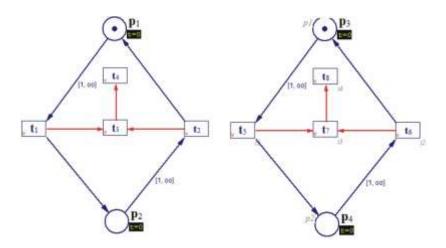

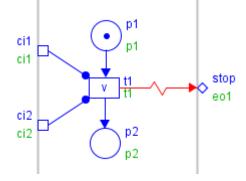

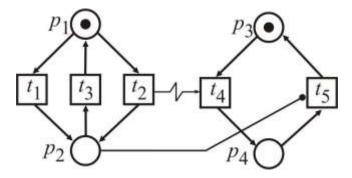

A Signal/Event net is a place/transition model similar to Petri nets [4-11]. Basic artefacts of the place/transition models are: *places*, which can bear *tokens*; *(net) transitions*, and *arcs* connecting places with transitions and transitions with places, known as *token flow arcs*. S/E nets in addition have two types of arcs: *event arcs* from transitions to transitions (e.g. (t2, t4)), and condition arcs from places to transitions e.g. (p2, t5). The model in Figure 1 is an S/E net.

A state of a place/transition model is determined by marking of its places, i.e. allocation of tokens across the places. Tokens can "flow" from state to state in some discrete moments according to the set of rules, known as "model semantics". Such a "jump" of tokens leads to a new state of the model, and is called *a state transition*.

It is said that net transitions can *fire* and transfer hereby tokens from a place to place.

Figure 4. A Signal/Event Net (book/example1).

#### 2.3 Semantics

The semantics of Signal/Event nets is defined by the firing rules of net transitions. There are several conditions to be fulfilled to enable a net transition to fire.

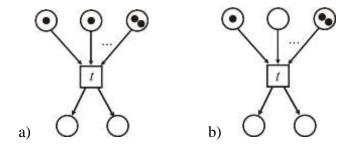

First, as in the ordinary Petri nets, an enabled transition has to have a token concession. That means that all pre-places have to be marked with at least one token as shown in **Figure 5** (or, in case of weighted arcs, with as many tokens as the weight of the corresponding arc from the pre-place to the transition.)

Figure 5. Token concession of transition: a) transition t has token concession; b) there is no token concession.

In addition to the flow arcs from places, a transition in S/E net may have incoming condition arcs from places and event arcs from other transitions. A transition is enabled by condition signals if all source places of the condition signals are marked by at least one token (more rigorously – as many tokens as the capacity of the flow arc), i.e. if more than one condition arc is connected to a place, the overall influence of the condition arcs is decided by the "AND" of each single arc enableness, as shown in **Figure 5**.

#### Modelling and Verification of Discrete Control Systems

**Figure 6.** If more than one condition arc is connected to a place, the overall influence of the condition arcs is decided by the "AND" of the each single arc 'enableness'.

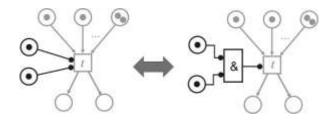

Another type of influence on the firing can be described by event signals which come to the transition from some other transitions in the net. With respect to incoming event arcs a transition can have either OR or AND mode (event signal sensitivity mode). The default event signal sensitivity mode of transition is OR, as shown in **Figure 7**.

Figure 7. The default event signal sensitivity function of forced transition is OR.

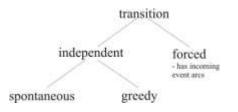

Transitions having no incoming event arcs are called *independent*, otherwise *forced*. A forced transition is enabled if it has token concession and it is enabled by condition and event signals.

Figure 8. Firing mode of transition.

Several S/E net transitions can fire simultaneously. A set of such simultaneously firing net transitions is called *step*.

A step is formed by first picking up a nonempty subset of enabled spontaneous transitions, and then by adding as many as possible of enabled transitions which are forced to fire by event signals produced by the transitions already included in the step. Such a step is called *maximal* with respect to its forced transitions.

#### 2.4 Conflicts and non-determinism

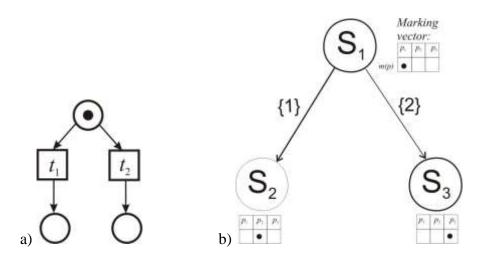

A *conflict* in classic Petri nets occurs when the number of tokens in some places is "not sufficient" to fire all transitions connected to them by flow arcs. This situation is exemplified in **Figure 9**, a.

Figure 9. Conflict (a) and reachability graph (b) (book/simple\_conflict).

In case of a conflict, not all transitions can fire simultaneously. The reachability graph in **Figure 9**,b shows that there are two steps 'fireble' in this state of the model:  $\{t1\}$  and  $\{t2\}$ . Since both these steps can happen, it is said that the choice is non-deterministic. In case if such a model is used for simulation either of this transition steps can happen. In the reachability graph, however, both options are included.

#### 2.5 Condition arcs

Tokens do not flow through condition arcs, so one place with a single token in it can enable many transitions and no conflict will arise, as illustrated in Figure 10 for the place p3.

Figure 10. Single token in p3 is sufficient to enable transitions t1,t2 and t3, so no conflict is observed in this situation.

#### 2.6 Arcs with capacities (weights)

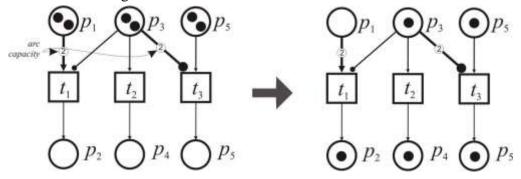

The token flow and condition arcs can have capacities determining the number of tokens that will flow through the arc (for token flow arcs), or needed to enable the corresponding destination transition (for condition arcs). If a source place has less tokens than is required then the transition would not get the concession. A net with arc capacities is illustrated in Figure 11.

Figure 11. S/E Net with arc capacities.

For example, the flow arc from p1 to t1 has capacity 2, and the condition arc from p3 to t1 has capacity 1. Both places p1 and p3 have 2 tokens, so the transition t1 is enabled. The transition t2 is enabled because it has only one flow arc from p3 and there are enough tokens in p3. The transition t3 is enabled because p5 has as many tokens as required (1) and p3 has as many tokens as required (2). Note, that only one token moved from p1 to p2 and one got lost since the capacity of the arc (t1, p2) is only 1.

Also note, that in the next state transition t3 would not be enabled although p3 still has one token. This is due to insufficient number of tokens in p3 to 'activate' the condition arc (p3,t3) which has capacity 2.

#### 2.7 State and reachability

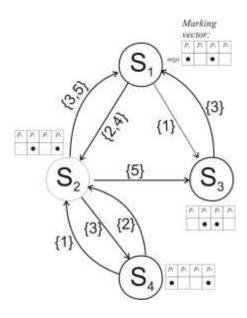

A state of an S/E net is defined by marking of all places. A tuple  $M = \langle Z, R, s_0 \rangle$  denotes the reachability structure of a S/E net, where Z is a finite set of reachable states, R is a finite set of *state transitions*<sup>1</sup>, and s<sub>0</sub> is an initial state.

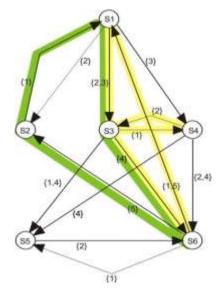

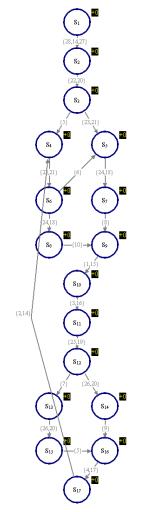

A state trajectory is a sequence of states  $(s_i) = s_0, s_1, ..., s_i, ..., s_i$ , such that for each pair  $s_j, s_{j+1} \in \mathbb{Z}$  there is  $\tau \in R$  such that  $s_{j+1}$  is reachable from  $s_j$  by the transition  $\tau$  (in mathematical terms denoted as  $s_j$  [ $\tau > s_{j+1}$ ). Figure 12 presents the reachability graph for the S/E net from Figure 4.

<sup>1</sup> Note the fundamental difference between net transition and state transition.

Modelling and Verification of Discrete Control Systems

Figure 12. Reachability graph of the model from Figure 4.

Nodes of the graph correspond to the states while the arcs correspond to the state transitions. The arcs are marked with their respective steps of net transitions.

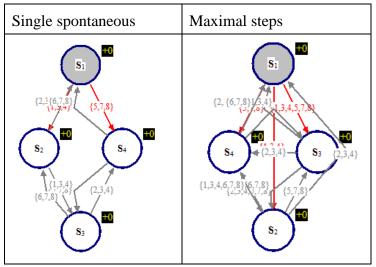

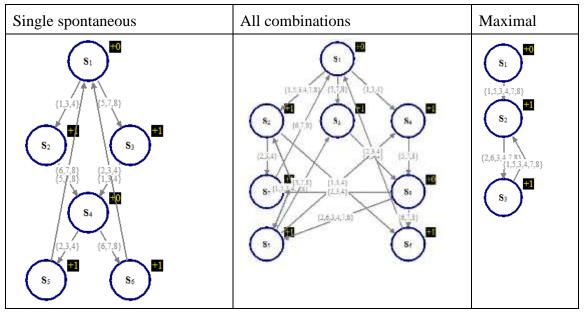

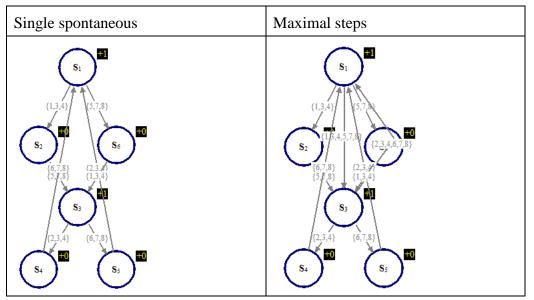

#### 2.8 State transition modes

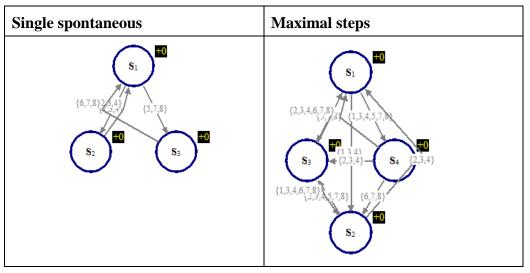

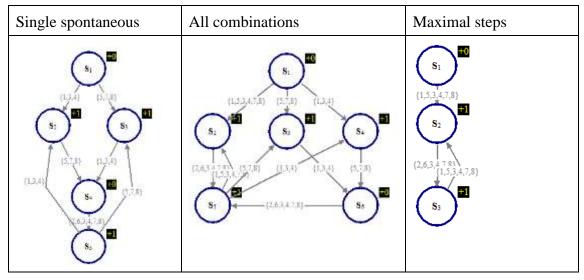

There are three ways to generate the transition step w.r.t. spontaneous transitions:

1. Include all possible combinations of spontaneous transitions (this was illustrated in the previous section in Figure 12);

2. Include only one spontaneous in a step (The corresponding reachability graph is shown in **Figure 13**, a);

3. Include maximum number of spontaneous transitions (the reachability graph is shown in **Figure 13**, b);

**Figure 13**. Reachability graphs of the model corresponding to a) single spontaneous transition; b) maximal set of spontaneous transitions.

In all cases forced transitions are included in steps according to the principle of maximal set of forced as discussed in the previous section.

#### 2.9 Synchronous transitions

There are special means provided for description of both asynchronous and synchronous behaviour in the same net, which are especially useful for modelling of interconnected plant/controller systems. This is achieved either by introduction of *synchronous* transitions, firing whenever they are enabled, or by timing.

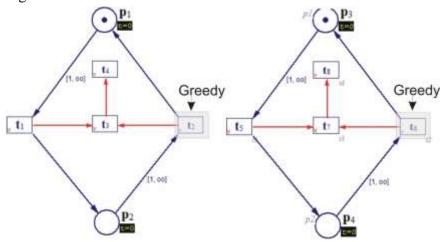

If a transition is marked with the synchronous (or greedy) attribute, it fires always when enabled. Synchronous transitions should not have incoming event arcs. When a firing step is formed, these are treated as spontaneous, with exception of that all enabled greedy transitions are always included in the step. Let us illustrate the work of greedy transitions on the example in **Figure 14**.

Figure 14. Reachability graph of the model with all spontaneous transitions.

As one sees, the model's behaviour includes all possible combinations of t1 and t2 with t3 and t4.

This example is provided in the Visual Verifier set of samples as TestSimple2Spont.xml. Check it with the options: Maximal set of greedy transitions and Combinations of spontaneous transitions as illustrated in **Figure 15**. The selected firing mode implies that all greedy transitions will be included in the step and all possible combinations of enabled spontaneous transitions will be added. If the set of Greedy is not empty, then the combination with empty spontaneous set will be also considered.

| 🖲 Options                                   |                   |    |  |  |

|---------------------------------------------|-------------------|----|--|--|

| SESA settings                               | Firing Rules View |    |  |  |

| Greedy Mode                                 | , l               | ie |  |  |

| I Model Timed<br>□ Recursive Model Checking |                   |    |  |  |

Figure 15. Selection of the firing modes in the Visual Verifier.

In the next example (Figure 15, TestSimple1Spont1Greedy.xml) two transitions are left spontaneous, while two others are made greedy. As a result, some trajectories have disappeared from the reachability graph.

**Figure 8.** In case if two transitions are spontaneous and two others are greedy, the possible step combinations are limited to those where a greedy transition is always included in the step.

If there is more than one greedy transitions enabled in the moment, they are included into step similarly to spontaneous transitions, i.e. steps are formed from all possible combinations of greedy, as shown in Figure 16, where all four transitions are greedy.

Figure 16. All transitions are greedy.

Note: The "greediness" of transitions can be only used in non-timed models. A similar concept can be achieved in timed models by using synchro sets introduced later in Chapter 14.2.

#### 2.10 Transitions without incoming arcs

A transition without any incoming arcs is always enabled.

#### 2.11 Priorities

In place-transition modelling formalisms a priority is an integer attribute of a transition determining preference of its firing with respect to other enable transitions. Only the transitions with the highest priority (from the set of currently enabled transitions) are included in the executable step. To avoid ambiguities, in S/E Nets priorities can be assigned only to spontaneous transitions.

#### 2.12 Firing rules

Visual Verifier supports several firing rules. The set of firing rules of SESA is a bit different. The reasons for having different firing rules are in the history of these tools. However, having several firing rules available may better fit to particular details of different models.

The firing rules of the Visual Verifier are as follows:

- single spontaneous can fire ;

- all combinations of spontaneous transitions will be considered;

- only the maximal combination of spontaneous can fire.

Certainly for each set of spontaneous transitions as many as possible forced transitions are added to form a step. This is called "maximum step".

In SESA two firing rules are supported:

- single spontaneous can fire ;

- all combinations of spontaneous transitions will be considered to form the maximum steps on their base;

In addition, the "greedy" transitions are treated in the VisualVerifier a bit differently from SESA.

In ViVe two options are provided:

- fire all enabled greedy transitions together or

- consider all combinations of the greedy;

This is applied 'on top' of the spontaneous firing rule.

In SESA greedy transitions are treated as normal spontaneous transitions.

## 3 Modular S/E Nets = Net Condition/Event Systems

The formalism of Net Condition/Event Systems (NCES) was introduced by Rausch and Hanisch in (*Rausch and Hanisch, 1995*) and further developed through the last years, in particular in (*Hanisch and Lüder, 1999*).

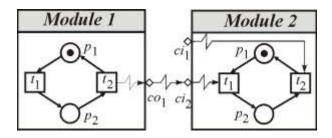

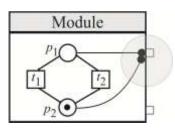

#### 3.1 Encapsulation of models into modules

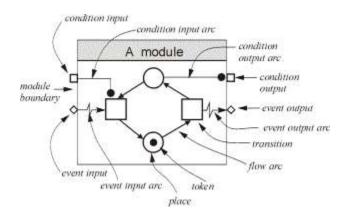

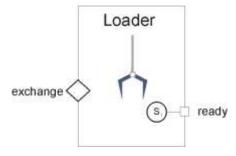

The general idea of Net Condition/Event systems supports the way of thinking of and modelling a system as a set of modules with a particular dynamic behaviour and their interconnection via signals. An illustrative example of the graphical notation of a module is provided in Figure 17.

Figure 17. Graphical notation of a module.

Once designed, the modules can be re-used over and over again. Each module has inputs and outputs of two types:

1. Condition inputs/outputs carrying information on marking of places in other modules, and

2. Event inputs/outputs carrying information on firing transitions in other modules.

Condition and event inputs are connected with some transitions inside the module by condition and event arcs. Places of the module can be connected to the condition outputs by condition arcs, and transitions can be connected to the event outputs by event arcs.

#### V. Vyatkin © 2007-2011

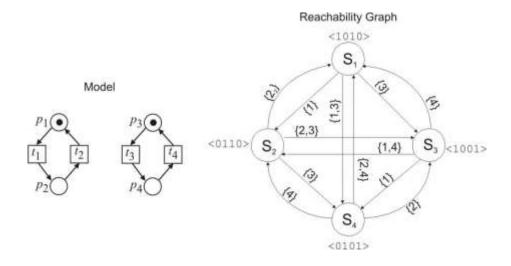

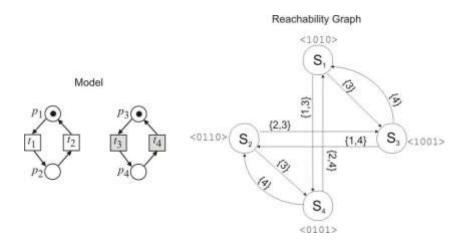

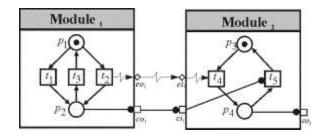

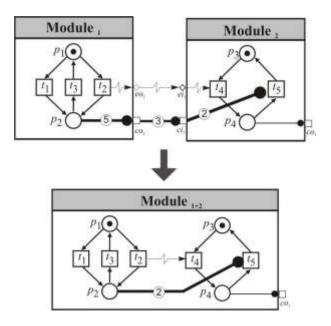

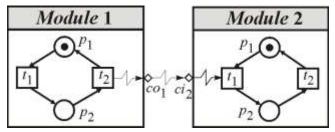

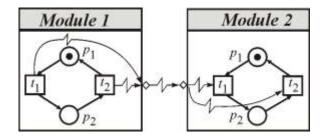

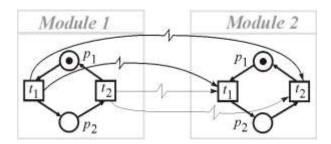

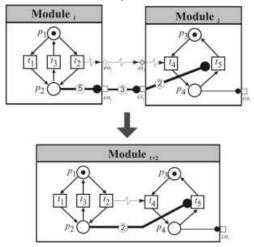

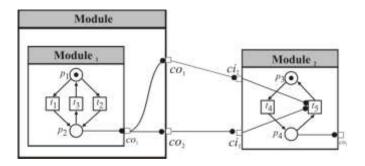

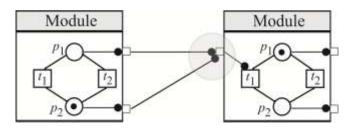

This concept provides a basis for a compositional approach to build larger models from smaller components. The "composition" is performed by "gluing" inputs of one module with outputs of another module as shown in Figure 18.

Figure 18. Modular composition.

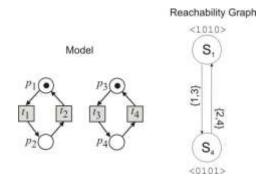

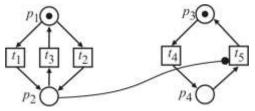

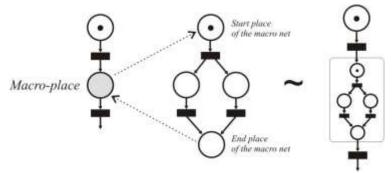

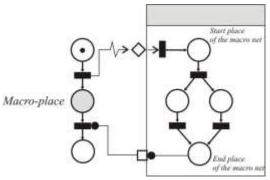

The result of the composition of two NCES  $N_1$  and  $N_2$  is an NCES  $N_c$  obtained as a union of the components and which can be represented as a new module. Inputs and outputs of the "composition" are unions of the components' inputs and outputs, except for those which are interconnected to each other, and hereby "glued", i.e. substituted by the corresponding condition and event arcs, as shown in Figure 19. By the way, the resulting module is equivalent to the S/E from **Figure 4**.

Figure 19. Result of the modular composition.

#### **3.2 Model type definition**

In the version of NCES implemented in Visual Verifier a model must be encapsulated in a module. A module is defined by its **interface** and **content**. The interface contains a model name and names of event and condition inputs and outputs. The content can be either a place-transition model, i.e. consist of places, transitions and arcs as described in the previous section (such model types are called **basic**), or be a network of modules interconnected via event and condition arcs (such models are called **complex**).

#### Modelling and Verification of Discrete Control Systems

Once defined and placed in the library, a module defines a **model type**. The module name serves as the type identifier. Type instances can be used over and over again in the complex models (strictly speaking, the modules forming the complex models have to be instances of other modules).

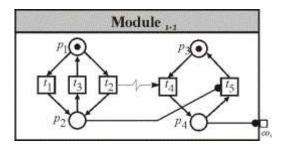

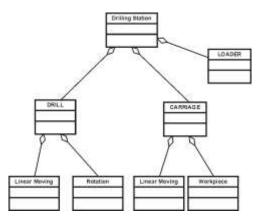

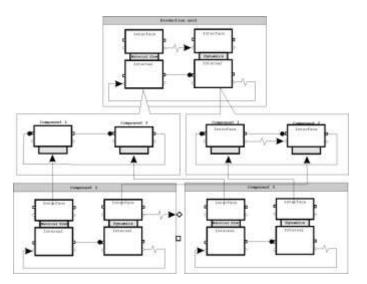

As a consequence of the above definition a model can have a hierarchical structure as the one presented in Figure 20. The hierarchical structure can be transformed into a plain S/E Net by instantiation of a model types.

Figure 20. A hierarchical NCES model.

Dynamic models of complex objects usually consist of models of their constituent components interconnected by event and condition signals. They may also include an additional model that integrates and coordinates them. Such a "master supervisor model" can also take care about input-output behaviour of the composite model.

#### 3.3 Typed NCES

Further in this text we are using only the typed NCES modelling. This approach is based on the following postulates:

1. All NCES models are encapsulated into modules. A *module* has *interface* that is defined by event and condition inputs and outputs. A modular model, stored in a separate file, defines a *model type* that can be later *instantiated*.

- 2. NCES models can be *basic* or *composite*.

- 3. A *basic* NCES model type consists of *places*, *transitions* and *arcs*. It **cannot** have any nested modules.

- 4. A *composite* NCES model type consists of *module instances* and *arcs* connecting I/Os of the modules to each other and to the interface elements of the model. The instances are obtained by instantiation of the model types, basic or composite, existing in a storage media (library).

The process of model development can follow both top-down and bottom-up approach. In the former case you may create new module interfaces and as needed specify them and store as model types in the library. After that you can reuse the models over and over again.

In the latter case you start with development of most basic model elements and save them as basic model types in the library. More complex models can be created as composite types using instances of the basic ones. This way you can create hierarchical models of arbitrary complexity always remaining flexible and reusing the repetitive submodels.

#### 3.4 Capacities of condition arcs

Condition arcs between NCES modules, or between a module and inputs/outputs of another module where its instance is included, can have capacities, that are integer numbers >= 1.

The capacities between modules can differ from the capacities of arcs within modules. When the modules are "glued" into a single S/E net, the capacities of resulting condition arcs are calculated as the minimum capacity of the segments forming them.

Figure 21. The capacity 2 of the condition arc (p2, t5) is obtained as the minimum of capacities of the arcs forming its segments within modules and between modules.

#### **3.5 Benefits of NCES**

There are two main reasons to prefer place-transition formalisms to many others formalisms, e.g. finite automata. The first is their non-interleaving semantics (i.e. possibility of firing several transitions simultaneously), which better fits to modelling of distributed processes and of their interaction.

Figure 22. Model of two processes as parallel composition of state machines or NCES.

The second reason is the more compact reachability space, explained as follows.

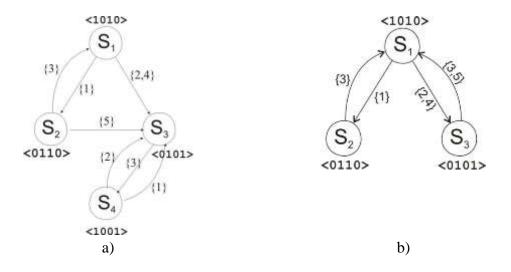

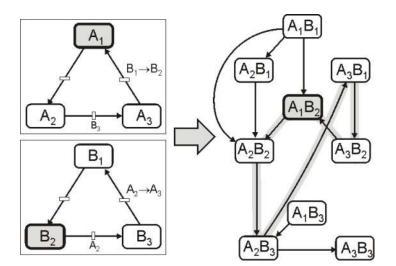

Modelling of complex distributed systems with automata usually ends up in many concurrent automata models communicating via common variables, as illustrated in Figure 23, left, where two state machines A and B are combined under "asynchronous parallel operator". Thus, the overall system model is a cross-product of the component automata, and to do model analysis it is necessary to build the cross-product consisting in this case of 9 states, as one sees in the right part of the Figure.

Figure 23. Modelling of two communicating processes by means of concurrent state machines and their cross-product automaton.

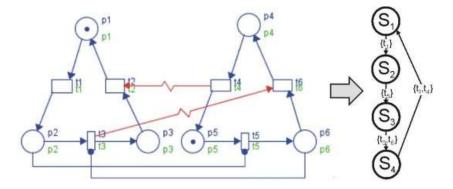

Alternatively, in Signal/Event Nets a state of a model is determined by the marking of model places, so any global state of a distributed system is just one state of the model. This is shown in Figure 24 where the same model is implemented in Signal/Event Nets with places  $(p_1-p_6)$  corresponding to states of the automata A or B (in the obvious manner) (Find it in the concurrent.xml file).

Figure 24. The same model implemented using place-transition nets (S/E Net) and its reachability graph.

In the given initial state the reachability space of the model consists of only 4 states. The same behaviour obviously will be shown by the automata model in Figure 23 (the outlined path  $A_1B_2 \rightarrow A_1B_2 \rightarrow A_2B_2 \rightarrow A_2B_3 \rightarrow A_3B_1 \rightarrow A_3B_2$ ), but to get it the whole cross-product automata needs to be built.

## 4 Semantics of Modular Models

The modularity of NCES does not bring any extra semantic issues if compared to S/E nets since the module boundaries are removed during the flattening process. However, some "tricky" issues in S/E nets and NCES semantics need to be discussed.

#### 4.1 A condition/event input of a module is not assigned

When an input is not assigned as shown in **Figure 25** there are several possible interpretations.

Figure 25. Not assigned input of a module.

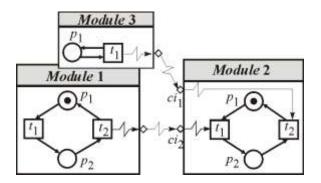

The one shown in Figure 26 removes the event arc  $(ei_1, t_2)$  making the transition  $t_2$  spontaneous.

**Figure 26.** First interpretation: the event arc is removed, transition t2 in the Module 2 becomes spontaneous.

However, this interpretation might not always reflect the intentions of the developer of the module 2, as the presence of the incoming event arc might indicate the forced nature of the transition  $t_2$ . Thus, the absence of any input arcs to the input  $e_i$  may mean that  $t_2$  should not fire at all. This can be implemented as shown in Figure 27 by adding a module (Module 3) with a transition ( $t_1$ ) that never fires, connected to  $t_2$  of Module 2. Modelling and Verification of Discrete Control Systems

Figure 27. Second interpretation: an always dead transition

#### 4.2 Multiple arc assignments to a module's input/output

Multiple arc connections to inputs and outputs of modules as those shown in **Figure 28** were not allowed in the previous versions of NCES due to ambiguities in interpretation.

Figure 28. Multiple assignments of arcs to I/Os.

However, since the signal arcs eventually influence the firing of transitions, we can shift the semantic load to the definition of the firing function of transitions, and interpret the concentration of arcs at inputs and outputs by connecting places/transitions in the resulting S/EN with an arc if a connected path exists from the corresponding source place/transition to the target transition in the original NCES. This is illustrated in Figure 29.

Figure 29. Signal arcs in S/E N as a result of multiple arc resolution in NCES.

#### 4.2.1 Condition arc weights between modules

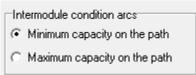

ViVe provides two options for resolving the weight of the condition arc appeared as a result of structural composition (Options/NCES tab).

Thus, if the first option is selected, the arc with the minimum weight determines the weight of the resulting arc after the assembly.

Figure 30. Multiplicity of the resulting condition arc.

#### 4.2.2 Several condition arcs originating in the same place

In process of assembly there could be a situation of several condition arcs ending in the same transition and originating in the same place.

Figure 31. Two condition arcs originating in p2 end in t5.

There are two options to resolve this situation. The first option is to take the maximum capacity across all paths leading from p2 to t5. The result in this case would be as shown in Figure 32.

Figure 32. Maximum path capacity is taken (1 in this case).

Another option is to assign the cumulative capacity to the resulting arc.

Figure 33. Sum of capacities is taken.

| 423   | Visual Verifier | support of no | n-assioned | module inputs |

|-------|-----------------|---------------|------------|---------------|

| 4.2.5 | visiai verijier | support of no | n-ussigneu | mounte inpuis |

| Ambiguous issue                           | Support in<br>ViVe | Interpretation                                                                |

|-------------------------------------------|--------------------|-------------------------------------------------------------------------------|

| Non assigned event input                  | Supported          | The destination transitions are connected to the "always dead transition"     |

| Non assigned condition input              | Supported          | The destination transitions are connected to the "always empty place"         |

| Multiple arcs to an event input or output | Supported          | The destination transition is connected to the transitions where the arcs are |

### V. Vyatkin © 2007-2011

|                              |               | originating from. |

|------------------------------|---------------|-------------------|

| Multiple arcs to a condition | Not supported |                   |

| input/ output                |               |                   |

Figure 34. Prohibited condition connections.

# **5** Timed models

### 5.1 Discrete timing

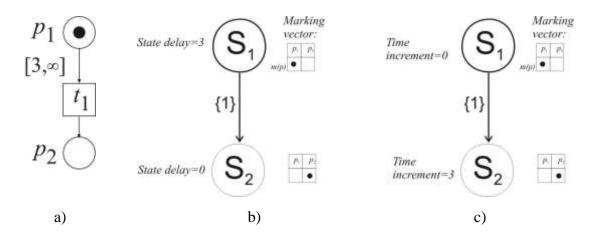

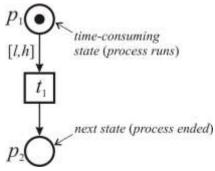

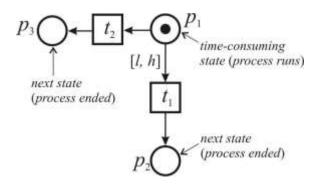

The concept of discrete timing is applied to the S/E nets as follows: to every pre-arc [p, t] of the transition t we attach an interval [l, h] of natural numbers with  $0 < l < h < \infty$ . The interval is also referred to as *permeability* interval. If a pre-arc has no explicitly designated permeability interval, it is assumed to be  $[0, \infty]$ . The interpretation is as follows. Every place p bears a clock u(p) which is running **iff** (if and only if) the place is marked (m(p)>0), and is switched off otherwise. All running clocks run at the same speed measuring the time the token status of its place has not been changed. If a firing transition t removes a token from the place p or adds a token to p, the clock of p is turned back to 0. A (marking-enabled) transition t is *time-enabled* only if for any pre-place p of t the clock at place p shows a time u(p) such that l(p,t) < u(p) < h(p,t).

An example is given in Figure 35.

Figure 35. Timed S/E net and firing of its transitions.

Thus, in timed NCES a state is characterized by the marking of places plus the values of local clocks at the places.

A state is called *dead* if no transition is time-enabled and no transition would become able to fire after any increments of the clocks.

There are two slightly different interpretations of time in different NCES implementations. Let us consider illustration in **Figure 36**, a.

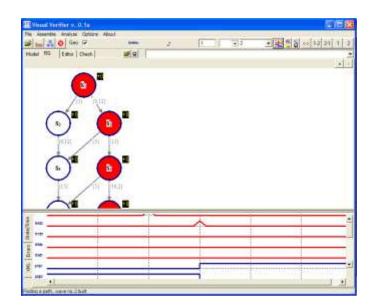

In one interpretation (implemented in SESA model checker), time delay is an attribute of the state where the transition originates. If in state  $S_i$  there is such a minimum increment  $\Delta$  that some of the transitions become enabled after elapsing it, then it is said that the state transition  $\tau:Si \rightarrow Sj$  has a "delay"  $\Delta$ . Conversely, it can be interpreted as the state  $S_i$  has a "duration"  $\Delta$  that specifies the time increment of the clocks of this state required to make the transition enabled. So, first the time elapses, and then a state transition occurs. This is illustrated in **Figure 36**,b.

Figure 36 An example of timed S/E net and reachability graphs for two time interpretations.

Another interpretation (implemented in Visual Verifier) uses the concept of time increment. This attribute belongs to the state where the state transition leads to. The reachability graph generated along with this interpretation is in **Figure 36**,c. This interpretation allows interpret the elapsed time as an (implicit) attribute of the state transition.

Although in this example, the number of states in both reachability graphs is the same, in general it can be different.

### 5.2 Firing rules in TNCES

At a given state all (time-) enabled steps have to be computed and placed into the list of enabled steps. Firing of each step brings one more state successor to the current state. Repetitive application of this procedure to every subsequent state forms the reachability space of the model. Time-enableness is a required but not sufficient condition to include transition to the firing step. The interpretation of the timing intervals is defined by the timing firing rule.

### Modelling and Verification of Discrete Control Systems

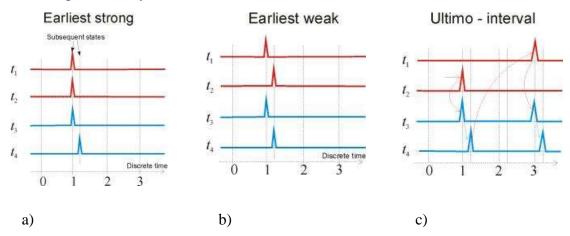

- 1. **Strong vs. weak firing**: with the *strong* rule all marking enabled (spontaneous) transitions, which have pre-places with clock position equal to either low or high time limit, are obligatorily inserted into the step (can be specified to make e.g. either strong earliest firing rule, or strong latest firing rule). If the *weak* rule is chosen then at least one of the enabled spontaneous transitions has to be included in step.

- 2. Earliest vs. interval firing: In case of the *interval* firing a transition is timeenabled at every clock position within the interval [l,h]. In the *earliest* firing rule a transition is time-enabled if it has a pre-place with the clock value equal to the low bound l of the time interval.

- 3. Ultimo firing: is a certain combination of the interval and strong rules: a transition is time-enabled at every discrete time moment within the interval and must fire at the latest at clock position equal to h.

In case if a transition has several incoming arcs with permeability intervals  $[l_1,h_1],[l_2,h_2],...[l_n,h_n]$  then, to enable the transition all arcs have to be permeable, which is achieved in the interval [l,h], where  $l=\max(l_i)$ ,  $h=\min(h_i)$ .

Among all possible combinations of time constants and time-firing rules, some were found of interest in some industrial applications. These combinations are presented in Table 1.

|    | Time<br>constants           | Firing rule      | Interpretation                                                                                                            |

|----|-----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1. | $l > 0, h \ge l$            | Interval, weak   | Event is expected with minimum delay $l$ , maximum delay $h$ , or may not occur at all.                                   |

| 2. | $l > 0, h \ge l$            | Ultimo           | Process must get terminated within the interval $[l, h]$                                                                  |

| 3. | <i>l&gt;0,h=∞</i>           | Earliest, strong | Process has duration <i>l</i> , and all simultaneously started processes with the same duration finish simultaneously     |

| 4. | <i>l&gt;</i> 0, <i>h</i> =∞ | Earliest, weak   | Process has duration <i>l</i> , but<br>termination of all processes with the<br>same duration may be not<br>synchronized. |

Table 1. Combinations of time-firing rule and time intervals commonly used for modelling.

The lower or higher time limits may or may not (depending on the corresponding rule) force transition to fire. The "interval" firing rule accepts presence of empty transition steps, when time elapses even in the absence of any enabled transitions. This option may be useful if aimed at finding of all possible combinations of overlapping processes and, correspondingly, simultaneous events. On the other hand it obviously explodes the reachability space. Perhaps, the variety of choices discussed in this Chapter is a bit confusing, but it extends the modelling horizons and allows more concise description of models. The following example explains the differences between firing options.

Figure 37. Timed version of a plant-controller interaction model

The following state-time diagrams illustrate different combinations of timed firing options. The earliest strong firing rule forces to fire all transitions when the low time bound is reached by clocks, at the earliest weak rule steps are formed from combinations of time-enabled transitions, at ultimo the firing may occur at every discrete time value within the permeability interval.

Figure 38. State-time diagrams representing different combinations of timed firing options.

# 5.3 Implementation

Not all timing modes are currently implemented in the available model-checkers.

# **5.4 Restrictions**

A transition with incoming timed arcs (i.e. [l, h] where l>0) cannot be forced, i.e. cannot have incoming event arcs.

# 6 Modelling of closed-loop controller-plant systems

An industrial automation system can be considered to be built from two conceptually different parts: controller and plant. The controller is a hardware device driven by software code that performs data processing, communication and decision making, the plant refers to the physical part of the equipment.

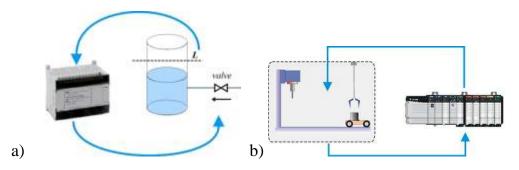

Figure 39 shows examples of such control systems. Figure 2, a shows control of the liquid level in a tank The tank has an input valve that controls the liquid supply. Once the tank is filled the valve should be closed. A level sensor (L) indicates the level where the filling should terminate.

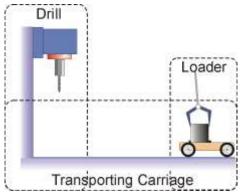

**Figure 39.** Examples of automated systems: a) control of the liquid level in the tank; b) manufacturing cell - an automated drilling station.

Figure 2,b presents a model of an automated machining process: drilling station. Modelling of automation systems can be done in either open-loop or closed-loop way. The open loop modelling usually is a more economical solution which bases on the partial model of controller inputs which help to generate the outputs and then verify their correctness.

#### Modelling and Verification of Discrete Control Systems

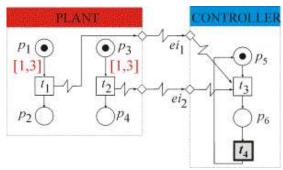

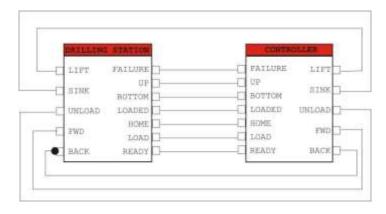

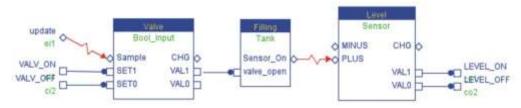

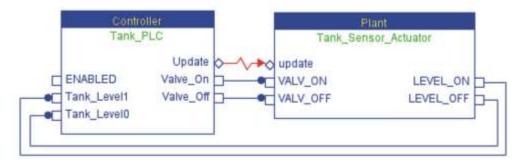

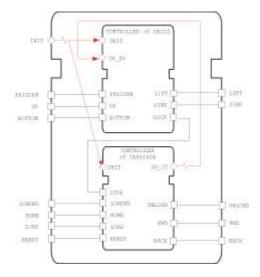

Figure 40 Closed-loop NCES model of the automated drilling station.

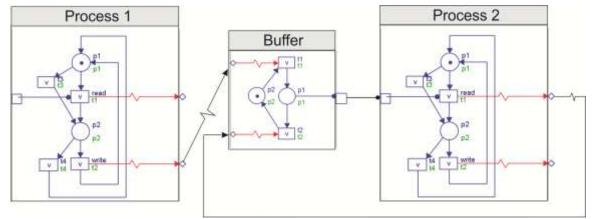

In the closed-loop approach exemplified in **Figure 40**, the model of the automated drilling station system is composed of two independent components: a model of the object (also known as plant) and a model of the controller, connected in a closed-loop by control signals and process data. Both parts are modelled using a common formalism. This approach allows for specification of desired/prohibited behaviour of the automation system in terms of the events/statements related to the object rather than in terms of input/output variables. The closed-loop approach is also beneficial in terms of complexity as a feasible model of plant restricts the controller's input combinations. The model of plant not only generates the inputs of the controller but also receives the outputs and correspondingly modifies its internal state.

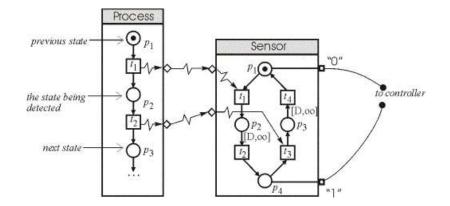

Certainly the latter approach is more complex as the modelling of uncontrolled reactive behaviour of objects is required. However its benefits overweight the extra work needed. Both parts of the system (plant and controller) are modelled by NCES modules with condition signal inputs and outputs. The connection between controller and plant is implemented via logic level signals which are modelled using condition arcs. Event signals are used in both models of plant and controller but not between them. In the model of plant events may be used, for example, to model the causal behaviour of sensors influenced from the observed processes. In controllers the event signals model the actions explicitly defined as event-driven (say, event-connected function blocks in IEC61499), as well as a lot of other internal operations: procedure calls, setting/resetting variables, etc.

The closed-loop approach allows for a number of application scenarios that can be derived from the diagram in Figure 41. The scenarios include source-code based modelling of the controller or controller prototyping by a model, as well as formal

synthesis of the controller. In all cases, the model of controller is combined with a manually created model of plant.

Figure 41. The framework for using formal methods in cyber-physical systems.

The prototyping scenario can be less resource-consuming during the validation if compared to the source code based model generation as the model of controller may cover only essential issues without implementation details.

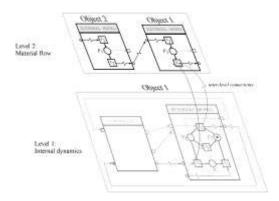

Depending on the accuracy of modelling, the model of plant may include components for each drive, motor, valve, electric relay, sensor, actuator, and other elementary pieces of equipment. These component models may be integrated to composite models of equipment units, such as machine tool, or other material processing and storage units.

Modelling of discrete controllers using NCES simplifies the assembling of the model from the components. Besides, such key features of NCES as event/data connections closely correspond to the latest trends in controller design methodology presented in the new international standard IEC61499.

# 7 Basics of Plant Process Modelling

## 7.1 Processes

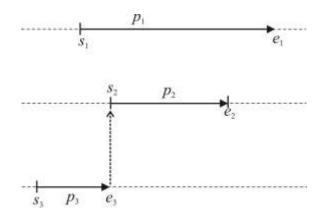

The behavior of a plant can be seen as a concurrent (usually asynchronous) composition of several processes, each of which has a start event s and ending event e, and some duration D.

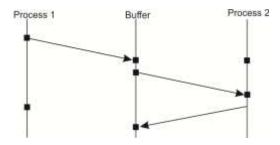

Figure 42. Asynchronous **c**oncurrent processes. Process 3 initiates process 2 by sending a message.

# 7.2 Simple process model

Such simple processes can be modeled by the S/E Nets as shown in Figure 43.

Figure 43. Model of a simple process.

Usually we model states of the plant components as S/E net places with safe (0/1) marking. In particular, for the processes with known minimal duration D>0 the time limits may look like l=D,  $h=\infty$ ; In this case the model contains no obligation for the action to occur.

If duration of action is not defined by an exact value, but bounded within the interval [D1, D2] (0<D1<=D2) then l=D1 and h=D2. In each state with clock value as D1<=clk(p1)<=D2 the action may finish, i.e.  $t_1$  may occur.

Combination [0, D2] is interpreted as "no minimal duration, but maximal time limit exists".

### 7.3 **Process with exception**

To model a time consuming action (i.e. with l>0) with exception possibility the initial place  $p_1$  is connected with two transitions: one of which stands for the normal operation mode with duration as described in the previous case, while the other models the exception, which interrupts the normal operation and may occur anytime within the normal operation time.

In case if  $h\neq\infty$ , the reached upper time limit forces only one of the transitions: either ending the action normally, or abnormally with an exception thrown.

Figure 44. Model of a state with an exception.

### 7.4 Two time scales: ticks in controller and time-elapsing in plant

Timing can be used in both plant and controller models to achieve adequate behavior of the model. In return it allows for quantitative time estimations, or for solving optimization problems like finding control strategy with minimal duration of the technological cycle, etc. Once all the NCES modules have been interconnected into Signal/Event Net, the resulting net has common time unit. That is why for modeling of objects with different time scale the minimum basic time unit over all components has to be selected.

Every time increment brings the model to a new state, which, obviously means state explosion if we try to decrease the basic time unit. This is especially sensitive in the closed-loop models. The common sense suggest to accept the time scale of the most relevant processes in the plant, and assume that processes in controller (or some electric units of the plant, such as sensors, or relais) as having zero duration.

However some estimations in controller still can be done by measuring the number of executed commands (or number of transitions in S/E N).

Figure 45. Program delay: model of the controller module which requires 100 commands for execution.

Modeling of a program unit which takes 100 commands for execution can be modeled as shown in Figure: initial place p1 is loaded with 100 tokens, and with every transition t1 one token flows from p1 to p2 through the flow arcs with multiplicity 1 until all the tokens come to p2. Then all the tokens come back to p1 in one transition t2 through the arcs with multiplicity 100.

# 8 Modelling Control Programs

Special industrial programming languages are applied for implementation of the control algorithms in Programmable Logic Controllers (PLC). The most of the known programming languages in the field were standardized in IEC 61131-3 in 1993 (IEC61131, 1993). The standard includes four programming languages: Instruction List (IL), Function Block Diagrams (FBD), Ladder Diagrams (LD) and Structured Text (ST), and a common element Sequential Function Chart (SFC) that serves for program organization into logical steps and expressing the transitions between the steps.

Despite the successful standardization of PLC programming, there is a number vendor specific programming approaches that have not been included in IEC61131-3, although they are quite popular in certain application areas.

A model of the controller can be built based on the source code of the control program. Relevant properties of system routines also have to be taken into consideration. The source code based validation gives an additional assurance in the correct behaviour of the system after commissioning.

The basics of the modelling of discrete controllers using place-transition formalisms were developed in *(Hanisch and Thieme, 1997)*. In general the modelling of controllers can be split into the following sub problems:

- Modelling of system routines such as scan cycle;

- Modelling of PLC execution is related to the performance of PLC hardware represented by times, instructions execution times, etc;

- Modelling of basic Boolean data and operations;

- Modelling of non-Boolean functions;

The use of NCES simplifies the assembling of the model from the components. Besides, such NCES features as event/condition connections closely correspond to the latest trends in controller design methodology presented in new international standard IEC61499.

The following examples serve to illustrate basic principles of mapping from commands of a programming language to NCES models.

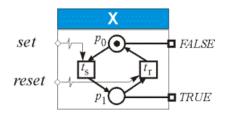

### 8.1 Data storage and assignment

Boolean variable cell can be modeled by the net having two places  $p_0$  and  $p_1$  and two transitions  $t_s$  and  $t_r$  as shown in the Figure 1. Setting of the variable is modeled by transition  $t_s$  and resetting by  $t_r$ .

assign resetreset reset res

Figure 46. Model of a Boolean variable implementing SET and RESET commands.

Figure 47 Model of a Boolean variable implementing also ASSIGNMENT of a value.

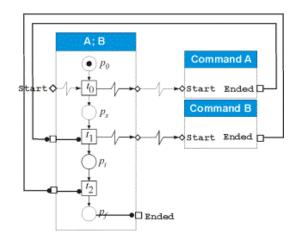

## 8.2 Linear sequence of commands

Consider how a linear sequence of two commands (e.g. A; B) can be modeled in NCES. Transitions  $t_0$ ,  $t_1$  correspond to the commands A and B. Once  $t_0$  fires it forces to start the model of the command A. Upon completion of A, the transition  $t_1$  starts the model of command B.

V. Vyatkin © 2007-2011

Figure 48 Model of a two commands' sequence.

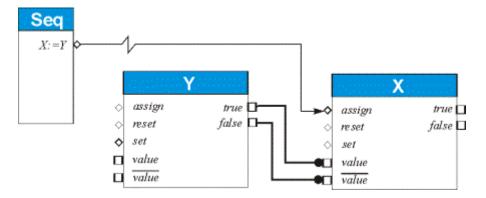

Figure 49. Model of an assignment operator.

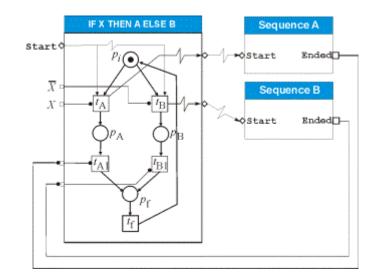

# 8.3 Conditional choice

Conditional choice of type **IF X THEN Sequence A ELSE Sequence B** can be modelled in NCES as shown in Figure 5. Transition  $t_A$  has incoming condition arc which relays value of X, and  $t_B$  has incoming condition arc marked with not X. Since the conditions are orthogonal, only one of the transitions is able to fire.

### Modelling and Verification of Discrete Control Systems

Figure 50. Model of a conditional choice operator.

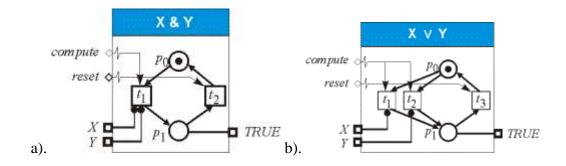

# **8.4** Boolean operations

Since every Boolean variable is modelled by two places (as was shown in Figure 46), we do not need a specific model for getting negation of a Boolean variable. As for the AND and OR operations, they can be modelled as shown in Figure 6, a) and b) correspondingly. Both models have two incoming event signals: *compute* and *reset*. Computation of the result takes one state transition.

Figure 51 Models of Boolean operations.

### 8.5 Subroutine call

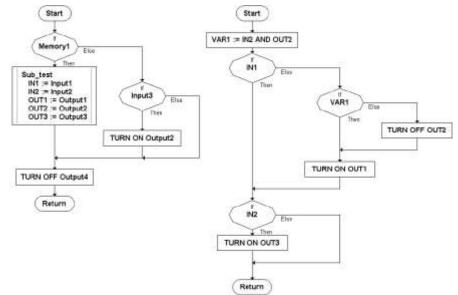

An example of a flowchart calling a subroutine is presented in Figure 52. The example includes modelling of the data that is passed to subchart, modelling of the Boolean operation, the subchart call and all the flowchart blocks.

Figure 52. Flowchart with a call to sub-chart

The main flowchart has a sub-chart call block, which invokes the sub-chart. The flowchart passes five variables: IN1, IN2, OUT1, OUT2 and OUT3 to the sub-chart. Four arguments of these variables are passed by reference, one argument passed by value and one is a local variable of the sub-chart. The modelling of the given flowchart and sub-chart starts with the modelling of the local and argument-by-value variables.

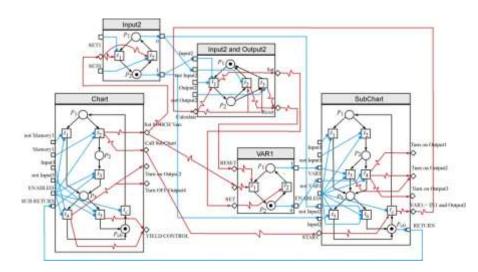

The resultant model is shown in Figure 53. For the sake of simplicity it shows only the modules modelling variables VAR1 and IN2, the module implementing the operation AND over two operands; and two modules representing the logic of the main and sub-chart respectively.

The NCES model of local variable VAR1 is modified as compared with the model in **Figure 46** as follows: an event input with an arc to the *t1* transition is added. The input provides variable reset at the moment when sub-chart is called. A NCES module is necessary for the variable IN2 due to its passing by value (although IN2 does not get modified inside the sub-chart in this example). It is modelled as the Boolean input similar to the model in **Figure 58**.

Thus, the local variables and the variables passed by value to the sub-chart are represented as independent NCES modules. Variables passed by reference are treated as global PLC variables and they can be modified directly by the sub-chart.

The NCES module corresponding to the main flowchart has two outputs that are related to the commands - "TURN ON Output2" and "TURN OFF Output4". All the other provide the representation of sub-chart call mechanism - "SET SUBCH\_VARS" and "CALL SUBCHART", and "YIELD" serves for yielding the control after termination.

Figure 53. Full model of the sub-chart and main chart.

The sub-chart module has an event input labelled as "START SUBCHART", which initiates the execution. The input is connected by event arc to the "CALL SUBCHART" event output of the main flow-chart module.

# 9 Co-existence of synchronous and asynchronous behaviour

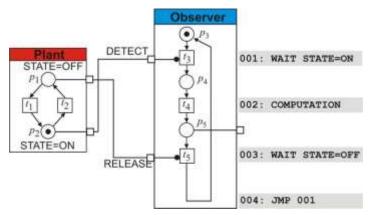

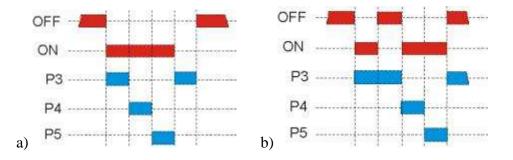

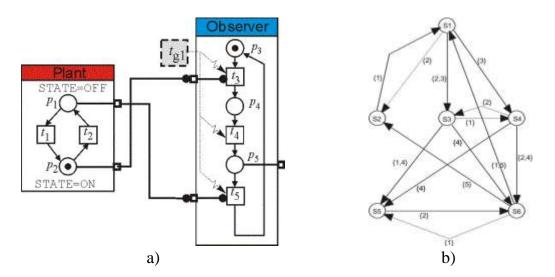

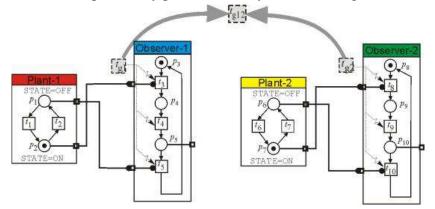

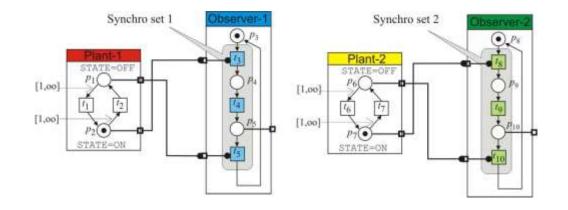

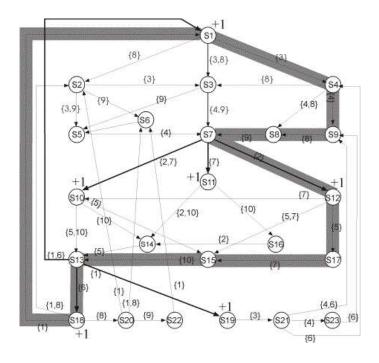

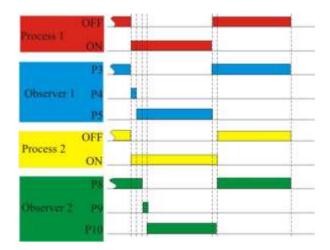

Usually transitions in models of plant represent start or finish of some time consuming actions, while transitions in the controller's part of the model represent almost instantaneously executed commands. Hence, when two transitions are enabled, one in the plant, and the other in the controller, first the latter has to be executed. Consider a simple example of process/controller communication as shown in Figure 54 (PlantObserverTest.xml).

Figure 54 Model of plant and observer.

The process is represented by the basic unit of plant which has two flip-flop states (as up--down, left--right, on--off) modelled by places  $p_1$  and  $p_2$ . The transitions t1 and t2 are spontaneous. First assume that the model is not timed (by ignoring the time intervals attached to the arcs).

The block "Observer" makes an "instant photo" of the process, i.e. reads the value of state in the loop (input DETECT) and when it is "ON" (i.e. m(p2)=1), performs some computations and stores the value in the memory. When the state becomes "OFF" (input "RELEASE"), the observer clears the memory and returns to the initial state.

Figure 55 Reachability graph of the model of plant/controller interaction.

If transitions in the observer were also spontaneous then, in the state shown in the Figure 54, there would be the following enabled steps of transitions:  $s1=\{t2\}$ ,  $s2=\{t3\}$ ,  $s3=\{t2,t3\}$ . However, the first step is not feasible: it reflects the situation when the event occurred (m(p2)=1), but the controller does not start the corresponding action though it was able to do so (was not busy), and the information about the action is lost.

**Figure 56** Desirable and incorrect sequence of plant/controller states. The sequence presented in the right Figure can never occur on the reality but is generated by the model.

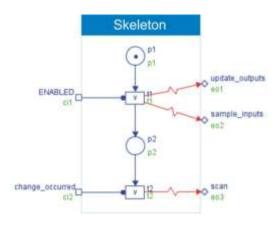

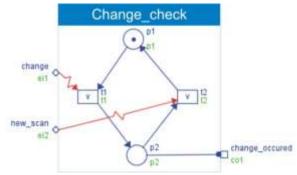

### 9.1 Non-timed models

The first, "greedy" transition approach is aimed at non-timed models. All spontaneous transitions in the controller (like those in the "execution logic" part) are marked as

greedy. According to the greedy firing rule, if a greedy transition is enabled, then each executable step must include at least one greedy. This guarantees that all enabled transitions (commands) in controller will be executed until the next action occurs in the plant.

Figure 57 Reachability graph of the interconnected system. Trajectories eliminated by the "greedy" tick generator are dotted.

To fix the behaviour of our model we introduce *greedy* transition **tg** connected to t3, t4, t5 via (dotted) event arc. Since **tg** is always enabled, it fires at every state transition sending forcing "ticks" to the commands in the controller no matter what is going on in the plant. All the transitions t3, t4, t5 could be marked as greedy instead and that would yield in this example the equivalent behaviour. But we prefer forcing such transitions from the greedy "tick" generator for the reasons which become clear in the next section.

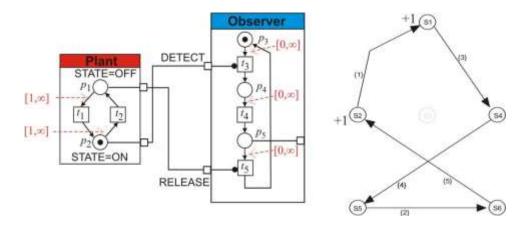

## 9.2 Timed models

In case of timed models, the use of greedy transitions in the former example is obsolete - the desired behaviour is obtained automatically since at the clock value u(p2)=0 (i.e. right after place p2 gets marked) the process in the plant is delayed, and the only enabled transition is t3.

The only possible sequence of firing is:  $t3 \rightarrow t4 \rightarrow (after 1 time unit) t2 \rightarrow t5$ , if all arcs in the controller model have zero-delay (i.e. time interval  $[0, \infty]$ ).

Figure 58 Timed model and its reachability gaph.

# 9.3 Testing timed NCES modules

For testing of timed models one may develop a structure similar to that in **Figure 58**, but with non-timed left "tester" module emitting random values in a loop. However, this will lead to the situation when the time is not getting incremented in the right, timed part of the model.

A cure can be to make the tester part also timed.

# **10Complete Example: Cylinder control**

# **10.1 Object description**

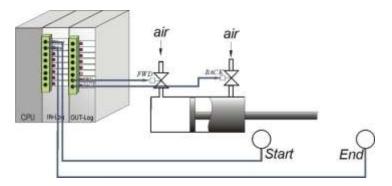

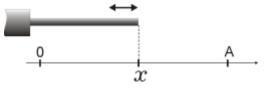

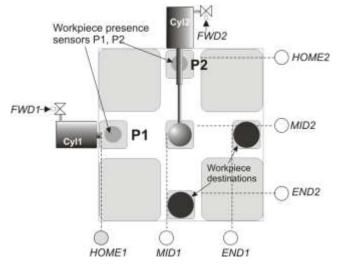

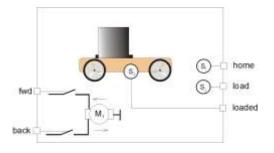

As the first example let us consider a very primitive control system of a single linear drive implemented using a pneumatic cylinder.

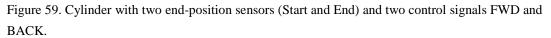

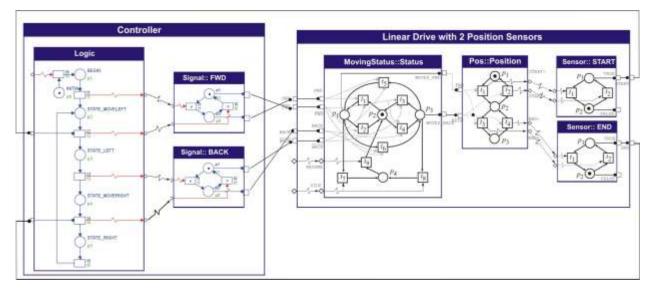

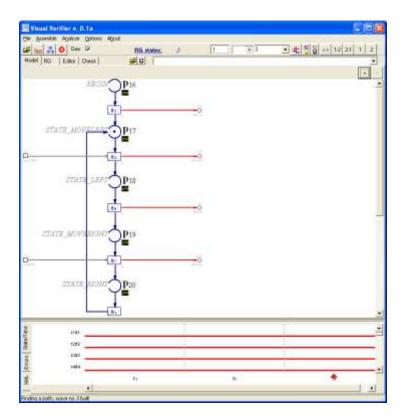

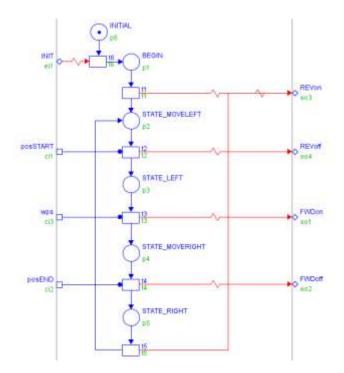

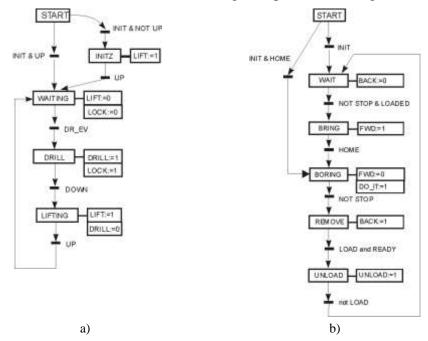

The operation of the object is straightforward. Suppose we want to retract the cylinder to its leftmost position and from there enter the eternal loop of moving forth and back. To achieve this suppose we write the following program in Sequential Function Charts (SFC) (as shown in the left part):

Figure 60. Control program in SFC language (a) and its model in NCES (b).

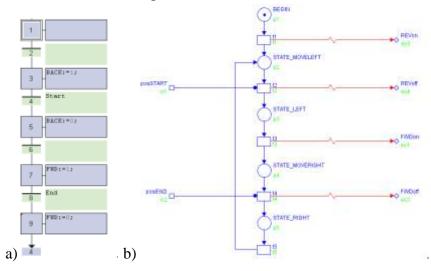

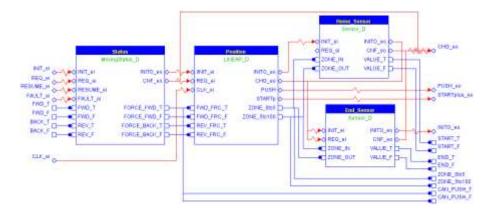

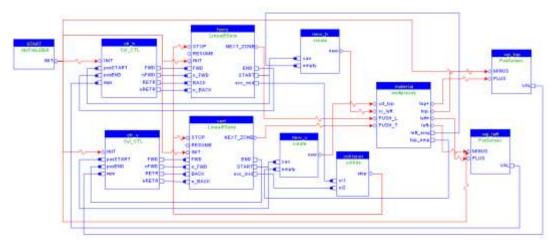

Now let us try to study this program applying the formal verification technique. For that we create NCES model of the controller, which is quite straightforward, the result is shown in Figure 60, b. Then we connect the model of controller with the model of plant as shown in Figure 61.

Figure 61. Block diagram of the Plant-Controller NCES model.

This model is provided with ViVe tool set and is called Cylinder.

### **10.2 Modelling the plant: Linear drive**

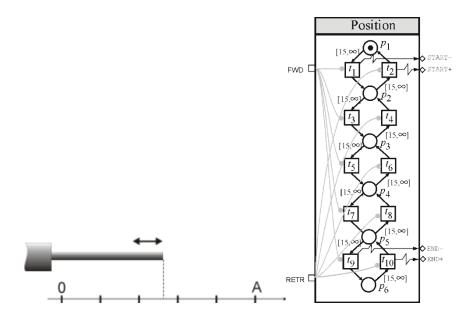

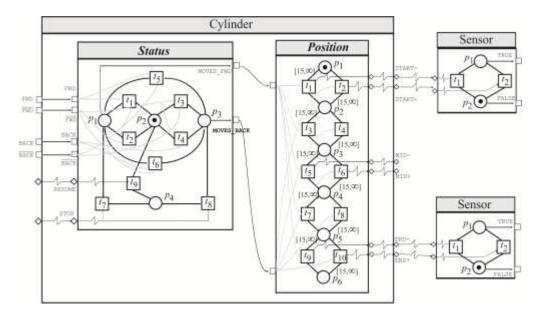

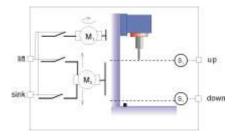

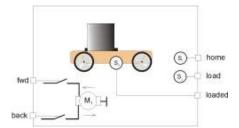

The most typical motion process in automated machines can be modelled and encapsulated for further re-use in the model of linear drive shown in Figure 62.

Figure 62. Linear drive.

The model which quite precisely represents uncontrolled behaviour of the drive is shown in Figure 63. Main modelled parameter is linear coordinate of the drive x.

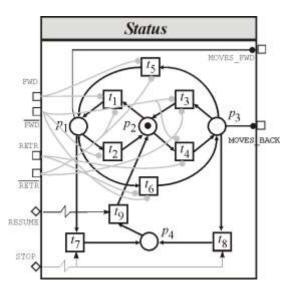

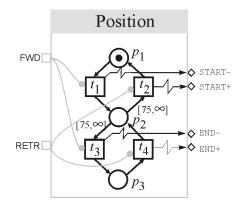

There are 6 states distinguished in the behaviour of drive, two of which are *dynamic* that means the speed is more than 0. The dynamic states are shown as circles, while the other *static* states are represented by rectangles with rounded corners. Model's inputs include two control signals FWD and RETR for forward and backward motion respectively. Input event STOP serves to relay all sorts of possible failure situations during the motion.

Figure 63 Continuous/discrete (hybrid) state-chart model of the linear drive.

The source of the failure is external to the model of drive, but consequence of the failure has to be taken into account within the model. According to the model, input event STOP leads to the static state "failure", and input event RESUME enables transition from that state to state "stop". The model above provides the numeric value of x as a function of time conditioned by the values of inputs.

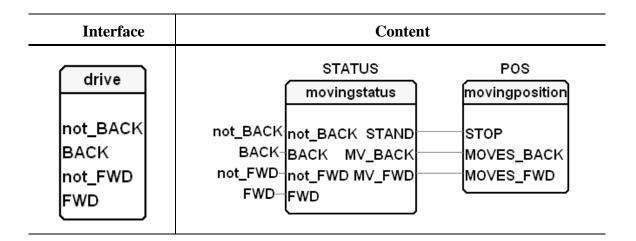

In order to represent similar model by means of a discrete state formalism we decompose functionality of the drive to most basic characteristics, for example as follows:

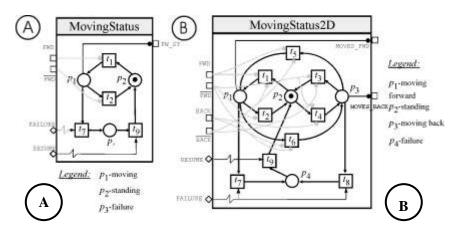

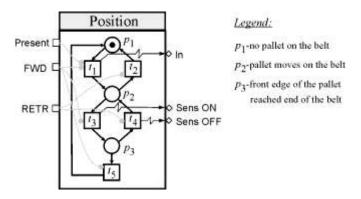

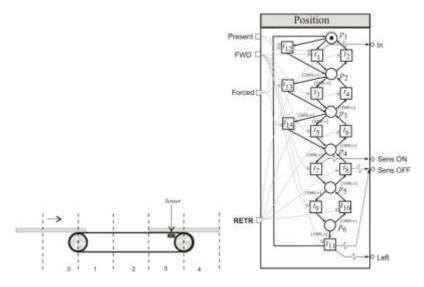

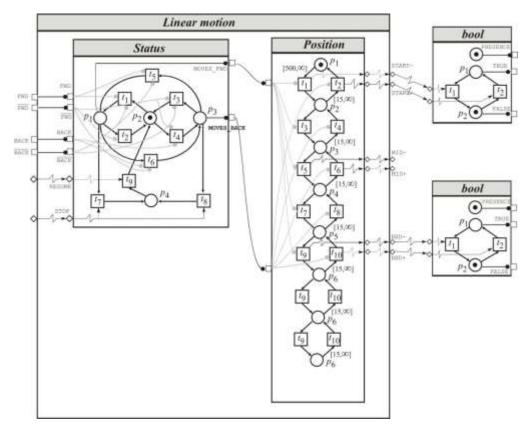

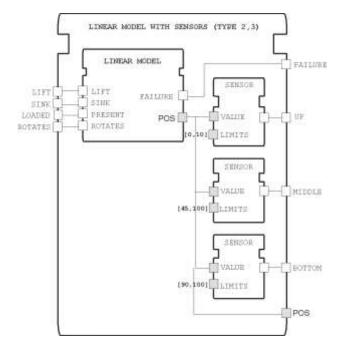

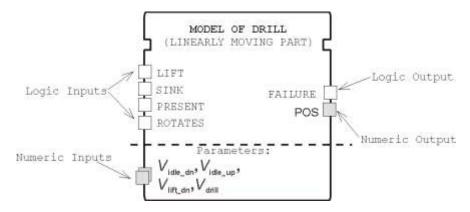

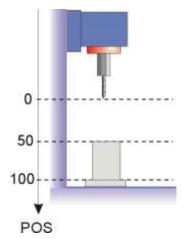

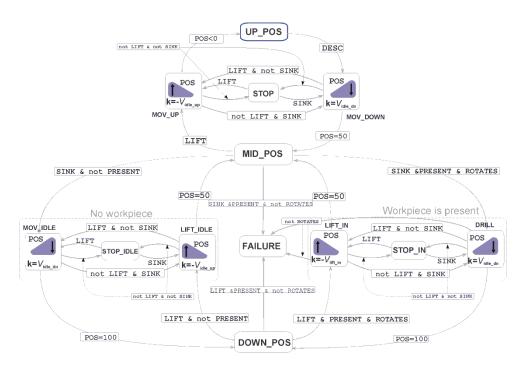

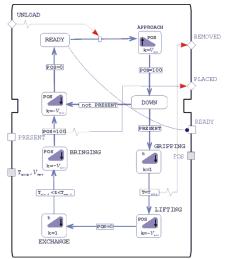

- motion status (stands ready to move, moves forward, moves back, stands in failure);